Contemporary wiring networks depend on advanced methods of load delivery and fault control that go far beyond basic copper circuits and mechanical relays. As engineering advances, so do the expectations for precision, safety, and efficiency in transmitting power to every load. From vehicles and industrial automation, understanding advanced distribution concepts is essential for designing and maintaining resilient electrical networks under all conditions.

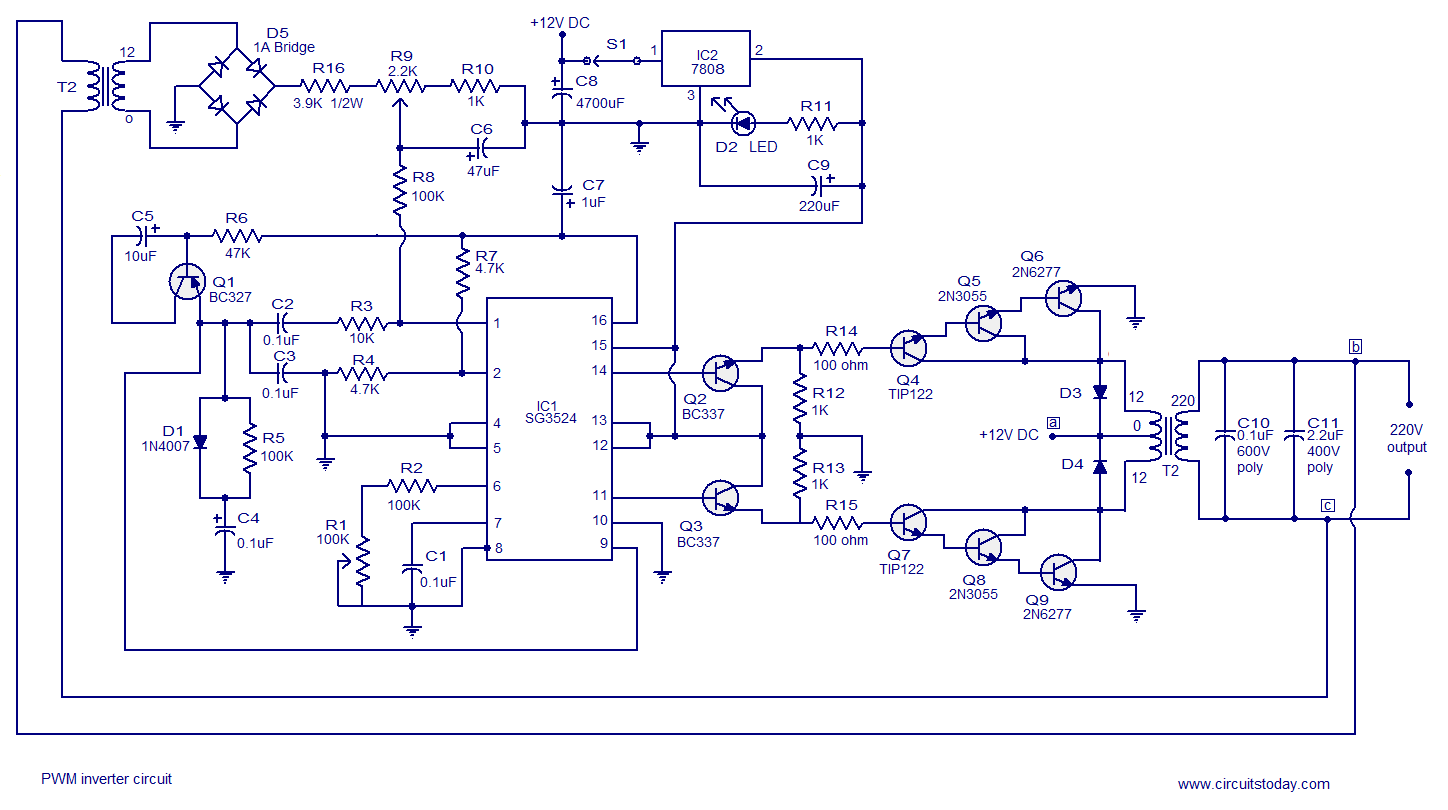

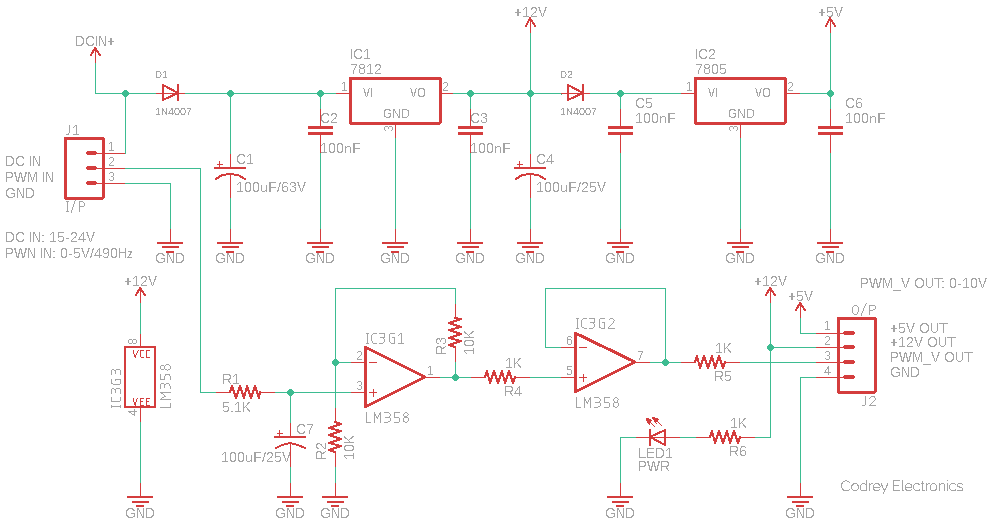

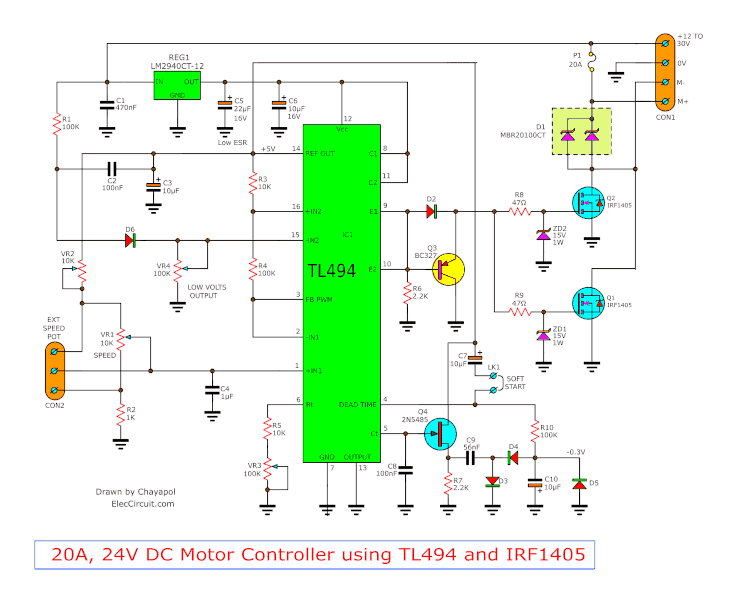

At its core, power distribution is the discipline of channeling energy from a single source to multiple destinations without excessive loss or imbalance. Traditional systems relied on electromechanical devices to manage power. While reliable for decades, these methods fail when facing microprocessor-controlled devices. To meet new operational standards, engineers now employ solid-state distribution modules (PDMs), digital fuses and smart sensors, and adaptive electronic protection that respond instantly to load variations.

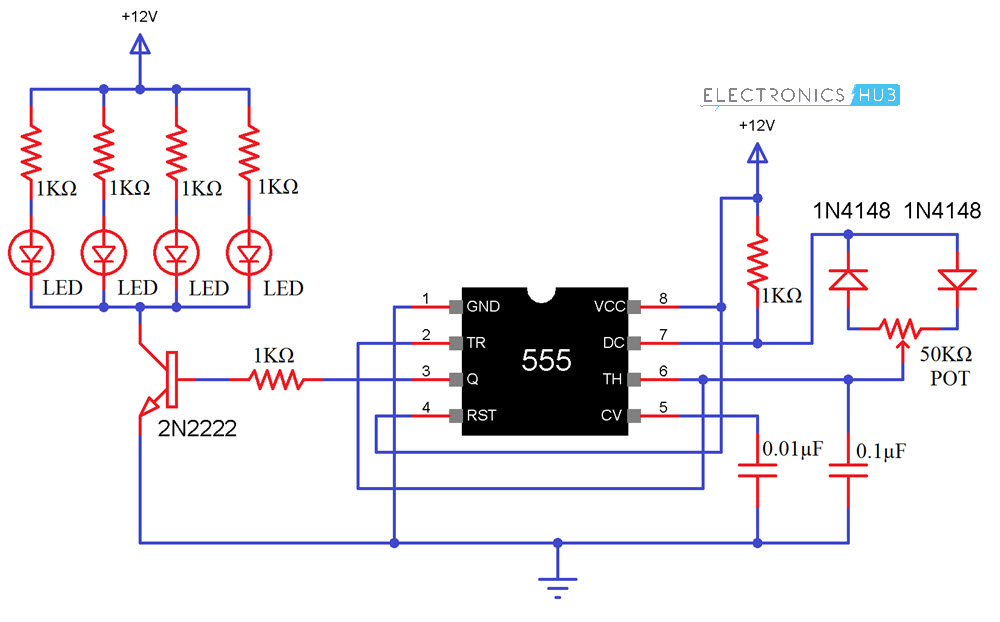

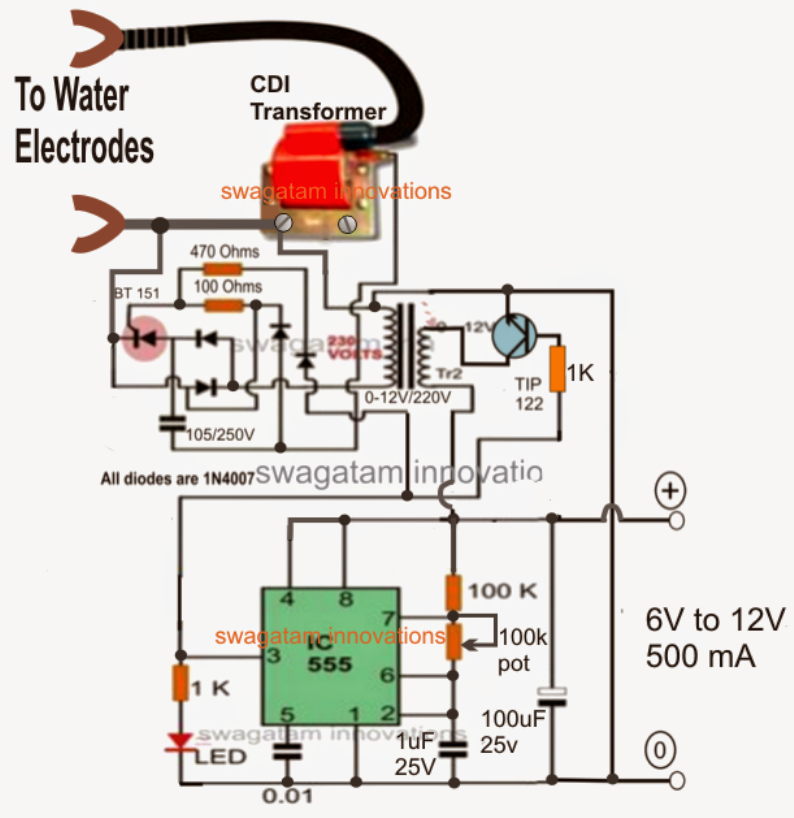

An digital fuse performs the same protective role as a conventional one but with added intelligence. Instead of melting metal, it interrupts flow through semiconductor logic, often within microseconds. Many e-fuses self-recover after the fault clears, eliminating manual replacement. Advanced versions also report data via CAN, LIN, or Ethernet, sharing status and fault history for deeper insight.

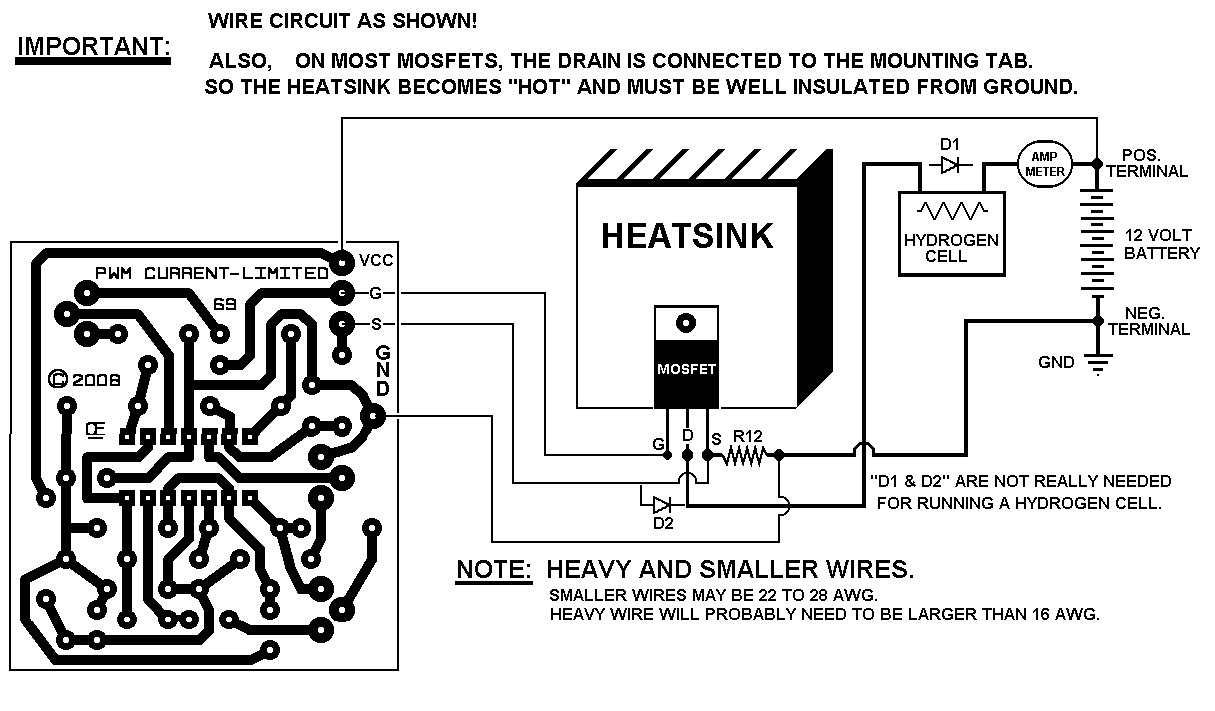

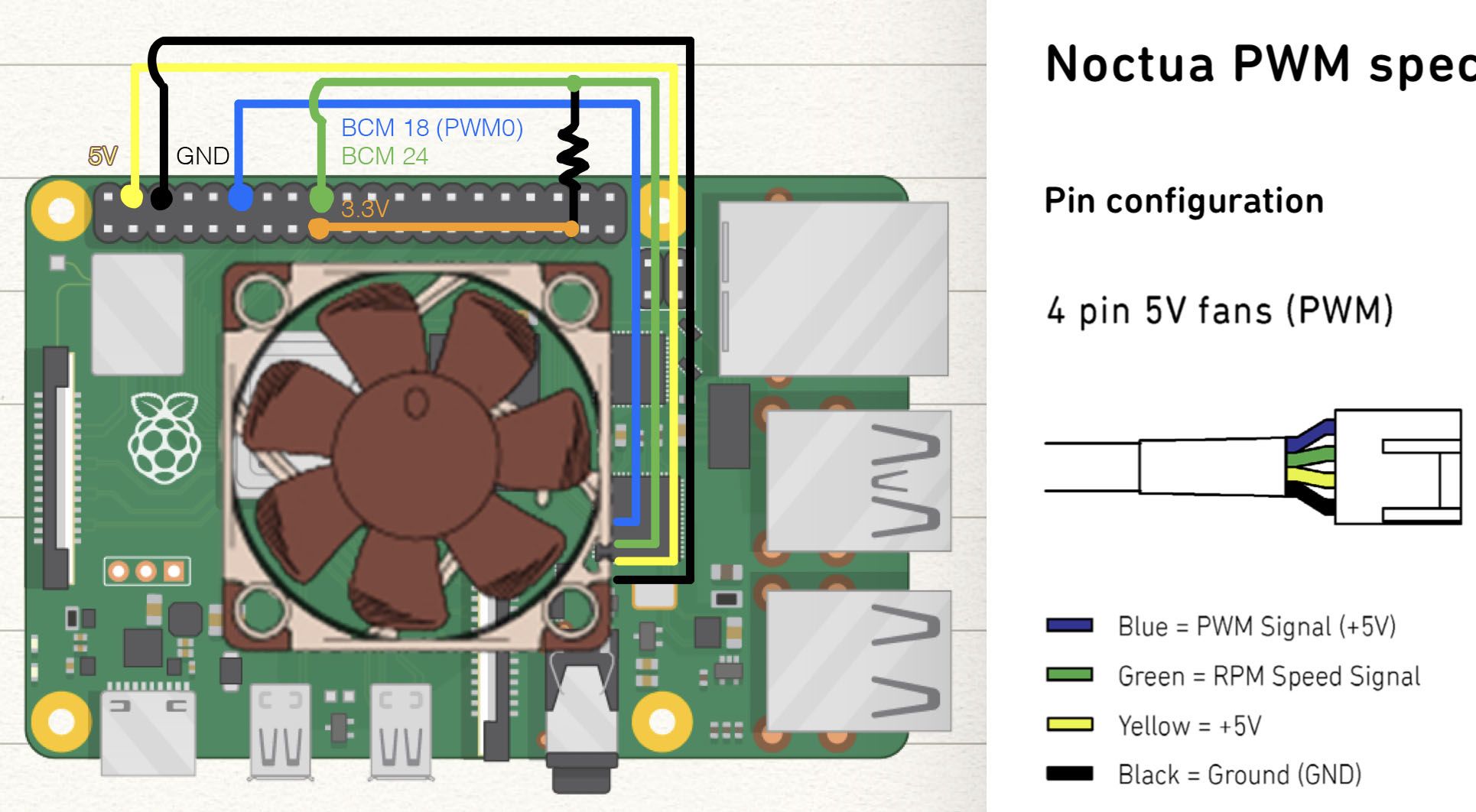

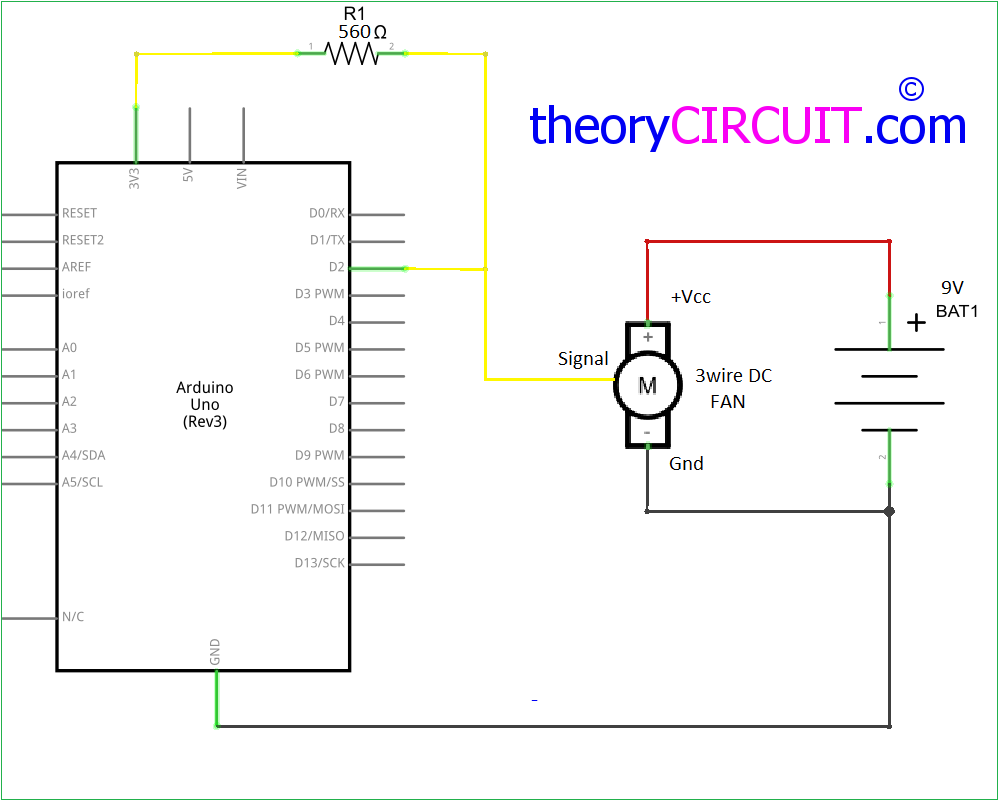

Solid-state relays (SSRs) have replaced mechanical contactors in many modern embedded applications. They operate silently, create less electrical noise, and suffer virtually zero arc damage. In environments subject to shock and harsh conditions, solid-state components outperform mechanical types. However, they introduce thermal challenges, since semiconductors generate heat under heavy load. Engineers mitigate this through careful design and cooling integration.

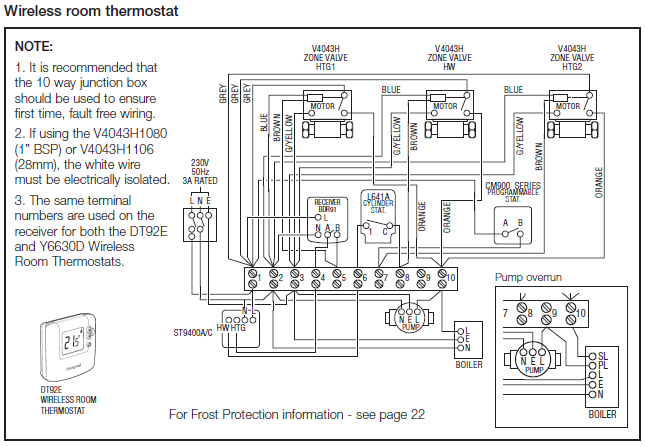

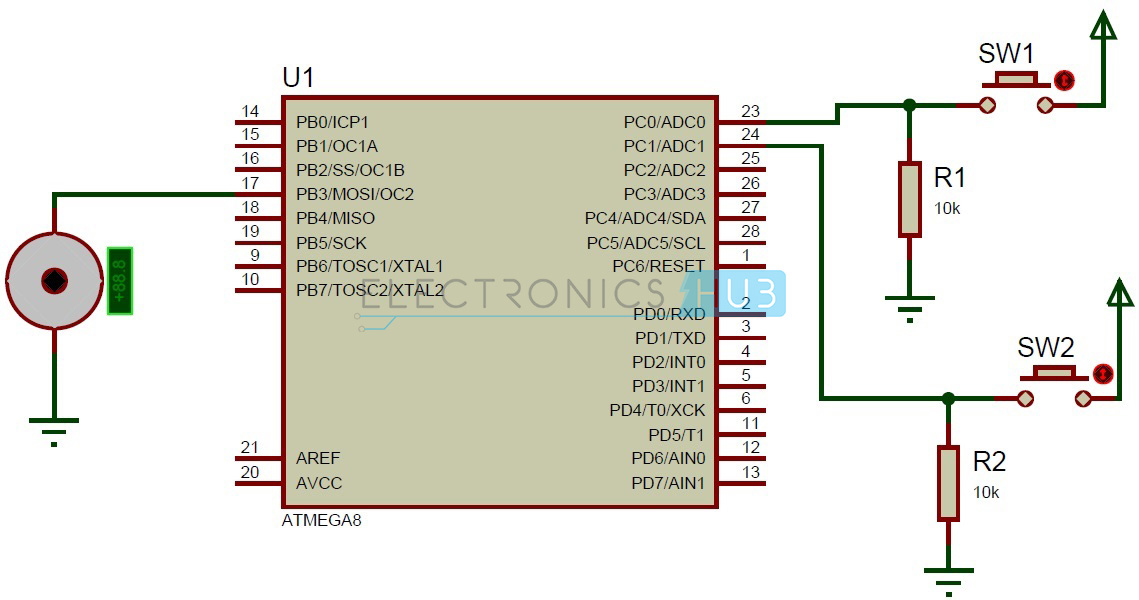

A well-structured power distribution architecture separates main, auxiliary, and control subsystems. Main feeders use busbars or heavy cables, branching into localized subnets protected by local fuses or limiters. Each node balances between safety and uptime: too lax, and fire risk rises; too strict, and false trips occur. Smart systems use adaptive thresholds that distinguish legitimate loads from anomalies.

Grounding and return-path design form the critical foundation of modern power networks. Multiple groundslogic, high-current, and safetymust remain isolated yet balanced. Poor grounding causes offsets, EMI, or data corruption. To prevent this, engineers implement controlled bonding networks, using low-impedance connections that maintain stability under vibration. Control units and sensors now track potential differences in real time to detect emerging imbalance.

The integration of digital power management marks a major shift in energy control. Microcontrollers within PDMs and switchboards measure real-time loads, log data, and control logic distribution. This intelligence enables predictive maintenance, where systems alert operators before breakdowns. Supervisory software visualizes current paths, fuse status, and system health across entire installations.

Protection components themselves have evolved. In addition to e-fuses, engineers employ polyfuses (PTC resettable fuses) and current-limiting breakers. Polyfuses self-limit current, resetting automatically after coolingideal for space-constrained electronics. Current-limiting breakers trip fast enough to cap energy before conductors overheat. Selection depends on load type and criticality.

Modern simulation tools enable engineers to simulate current paths and protection timing before hardware is built. By analyzing voltage drop, conductor temperature, and fuse response, they ensure safe power margins under all conditions. These digital models lead to more reliable designs with longer lifespan.

From a maintenance view, smart distribution simplifies troubleshooting and monitoring. Built-in diagnostic channels record overcurrent events, pinpoint fault locations, and allow virtual reconnection without physical access. This is invaluable in hard-to-reach installations, reducing service time and cost.

Despite new technologies, the principles remain timeless: power distribution is still about directing current with precision. Whether through copper conductors or silicon switches, each design must protect the circuit, contain failures fast, and maintain traceable schematics.

In the broader engineering context, advanced distribution and modern fusing techniques represent the evolution of classical wiring. They show how mechanical design, electronics, and software now combine to form adaptive systems that are not only protected but also capable of monitoring their own health. Through these innovations, engineers balance reliability with intelligence, ensuring that energy continues to flow stably and safely.