In electrical engineering, precision does not end when the last wire is connected. The long-term safety, reliability, and maintainability of any system depend on its level of documentation, identification, and verification. Without structured diagrams and traceable markings, even an advanced control system can become unmanageable and error-prone within months. Documentation and quality control transform a wiring job into a professional system.

### **The Role of Documentation**

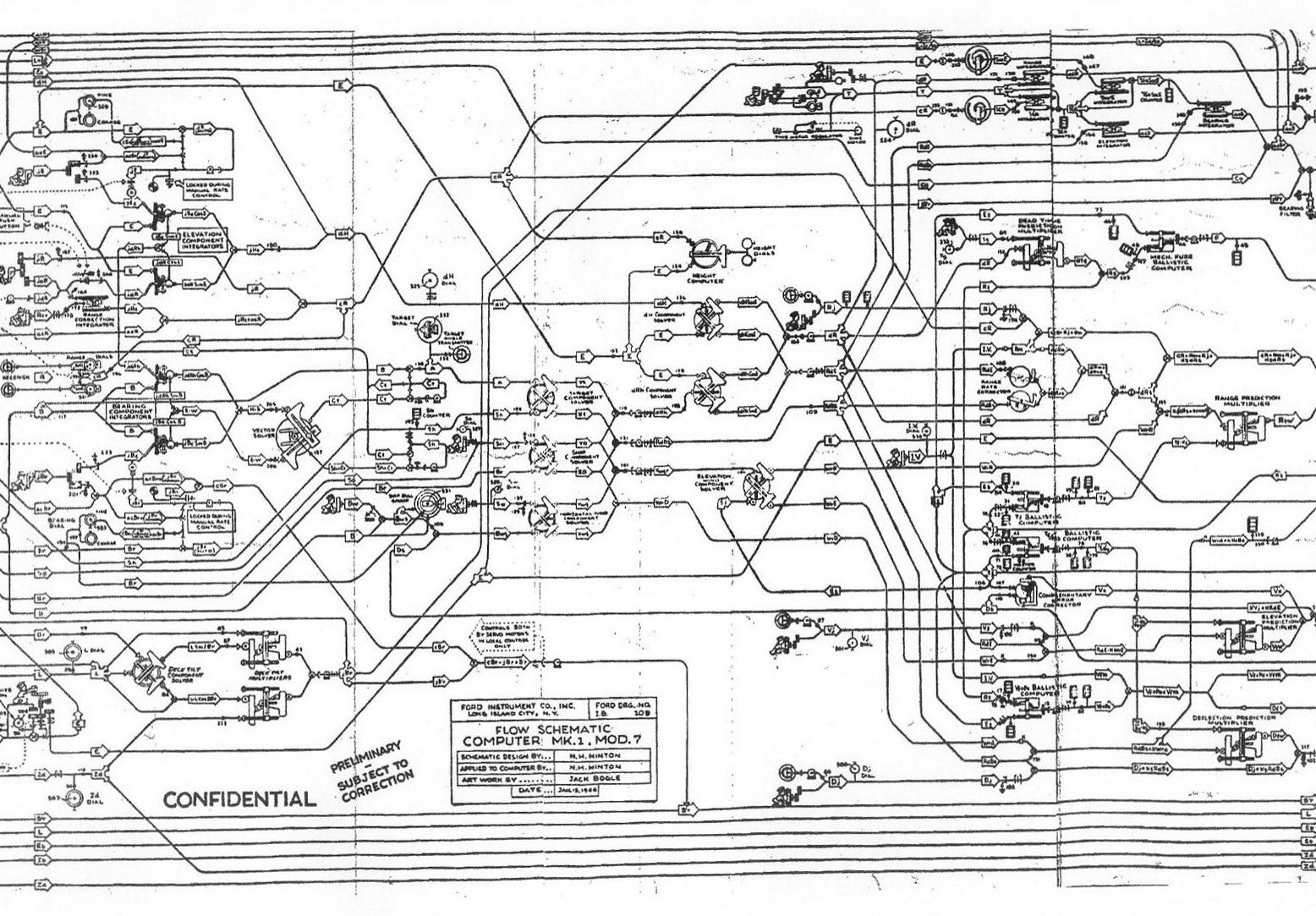

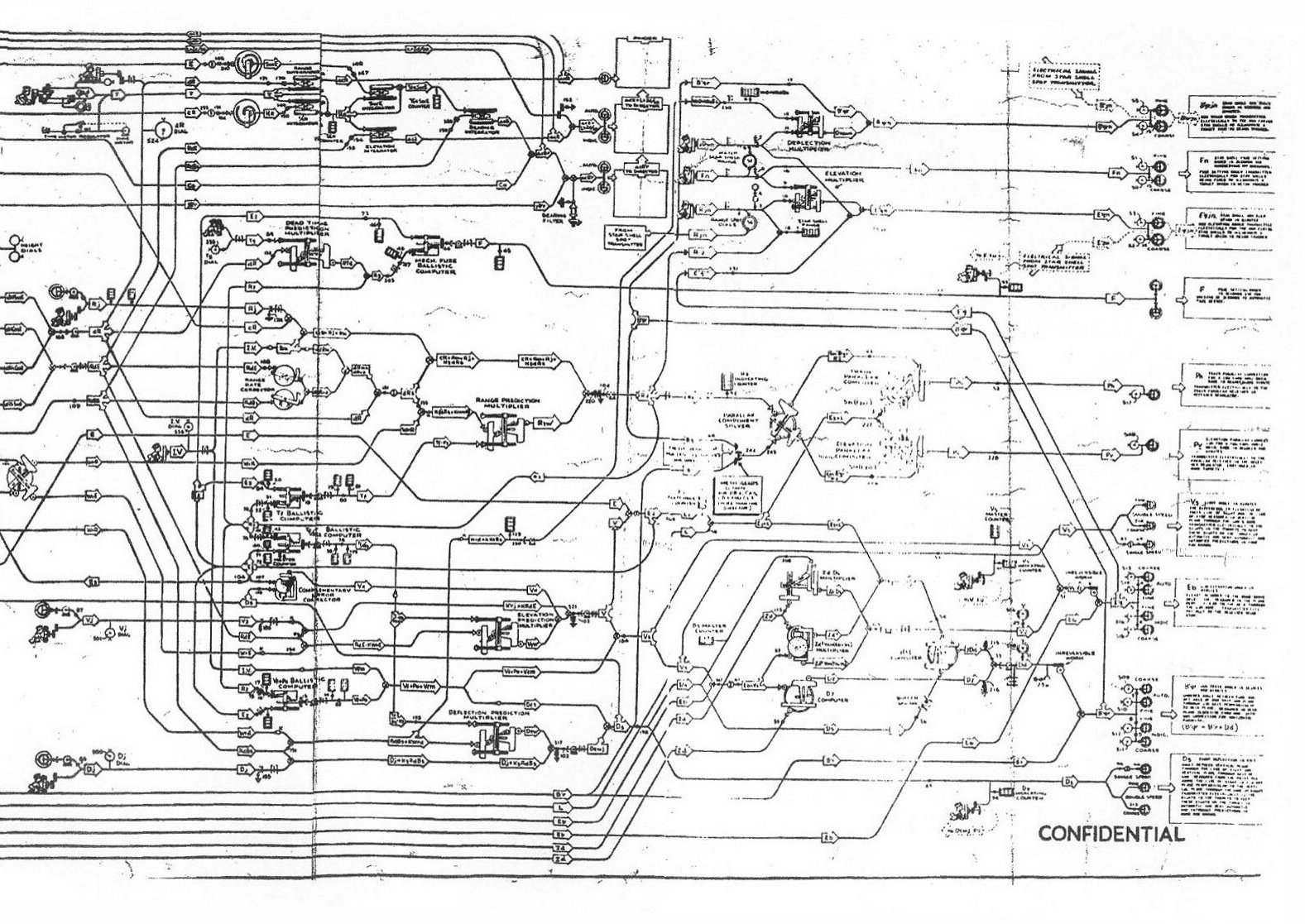

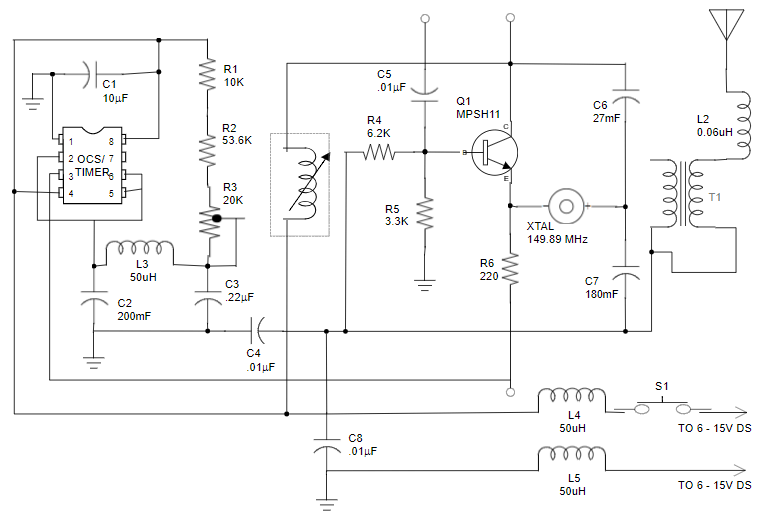

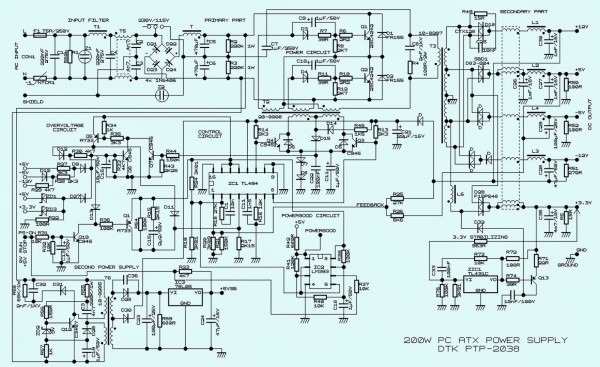

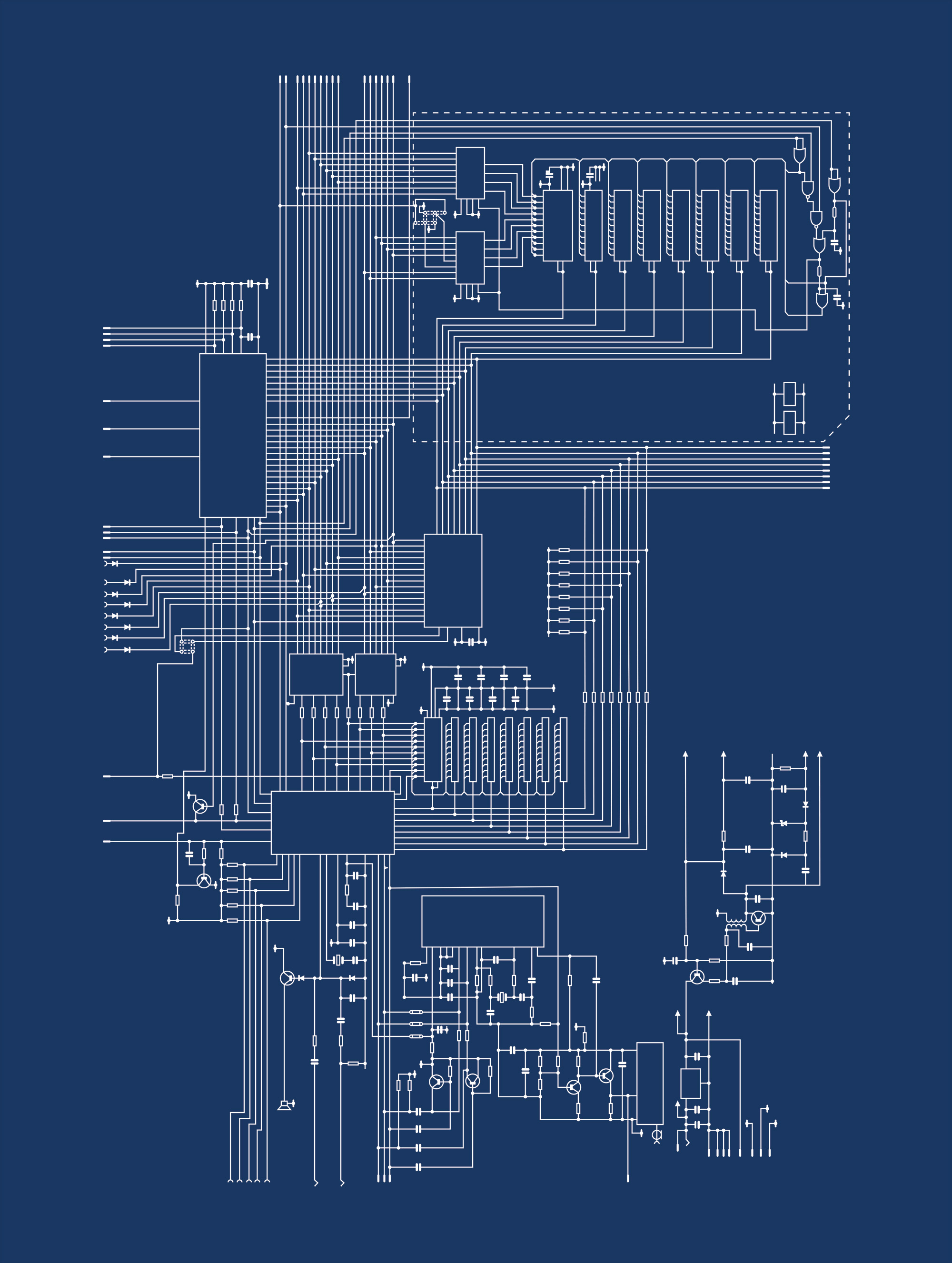

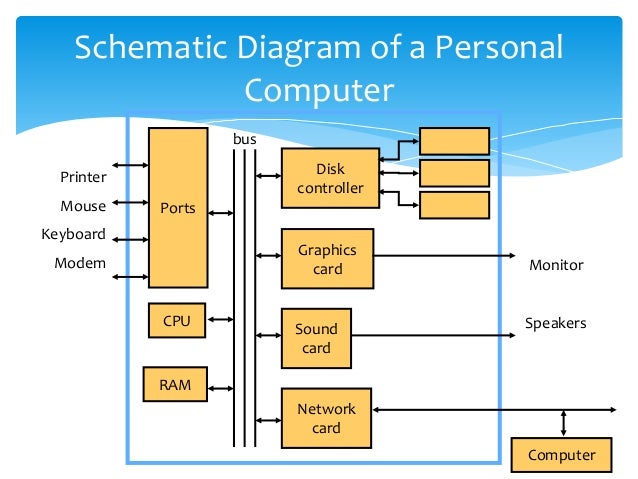

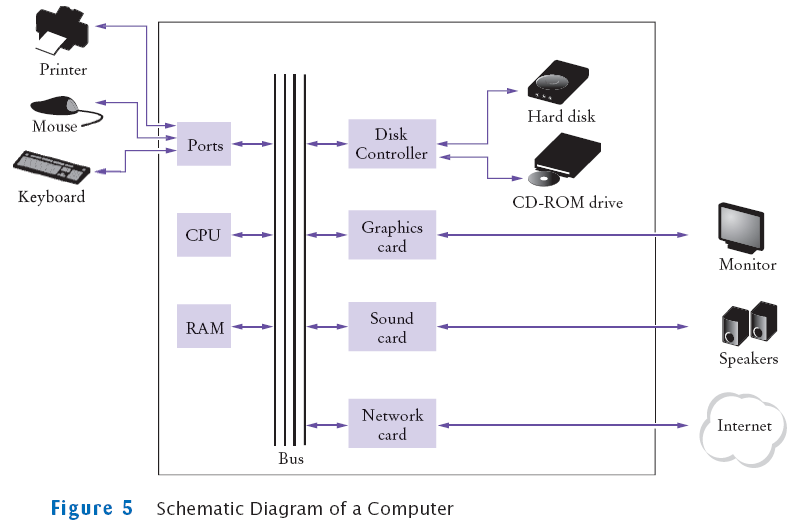

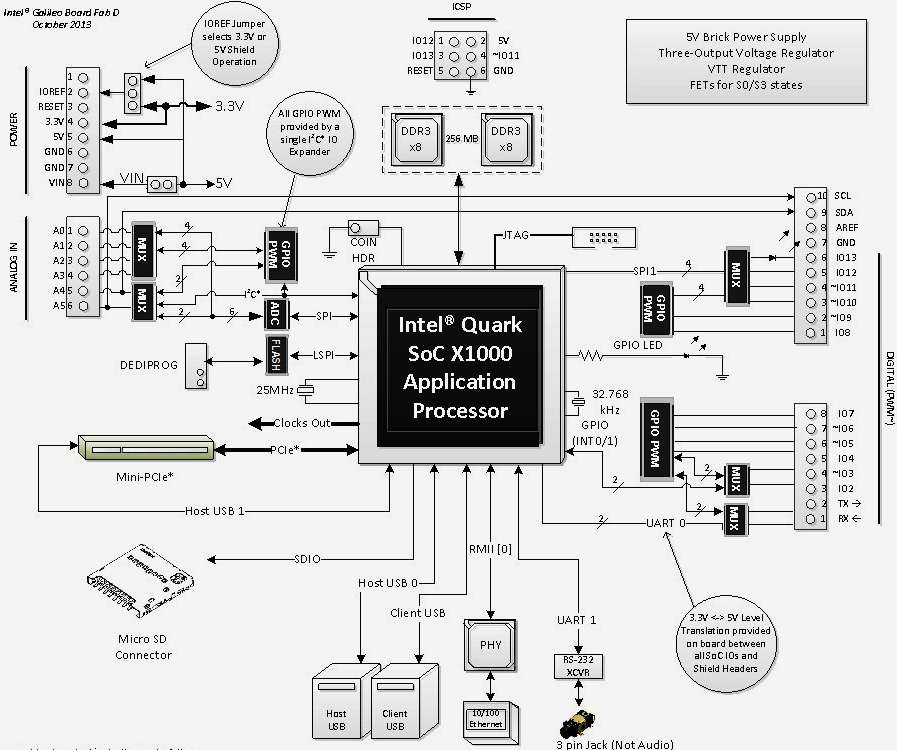

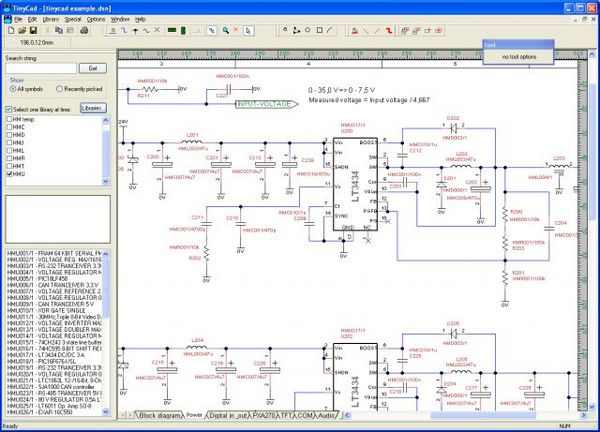

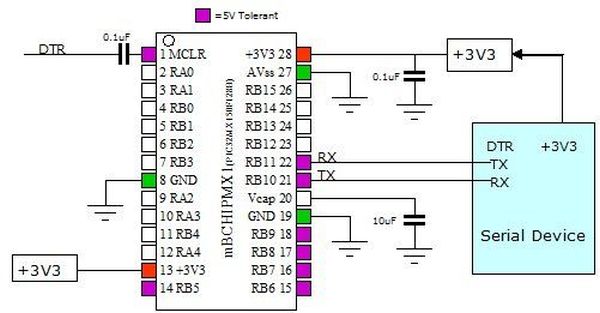

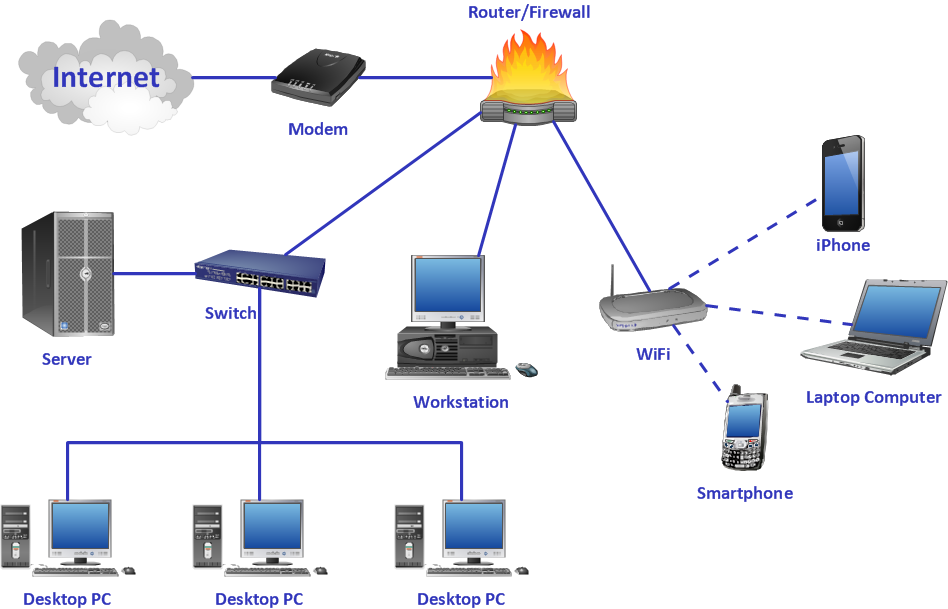

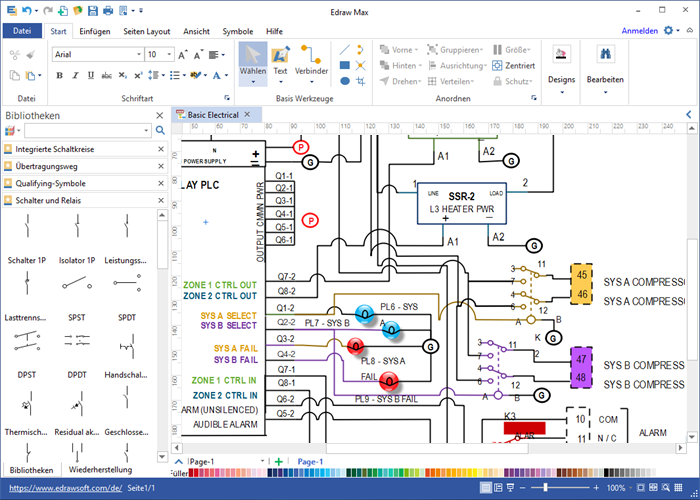

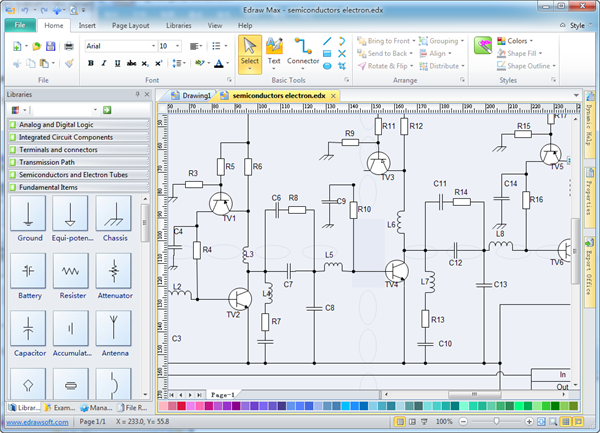

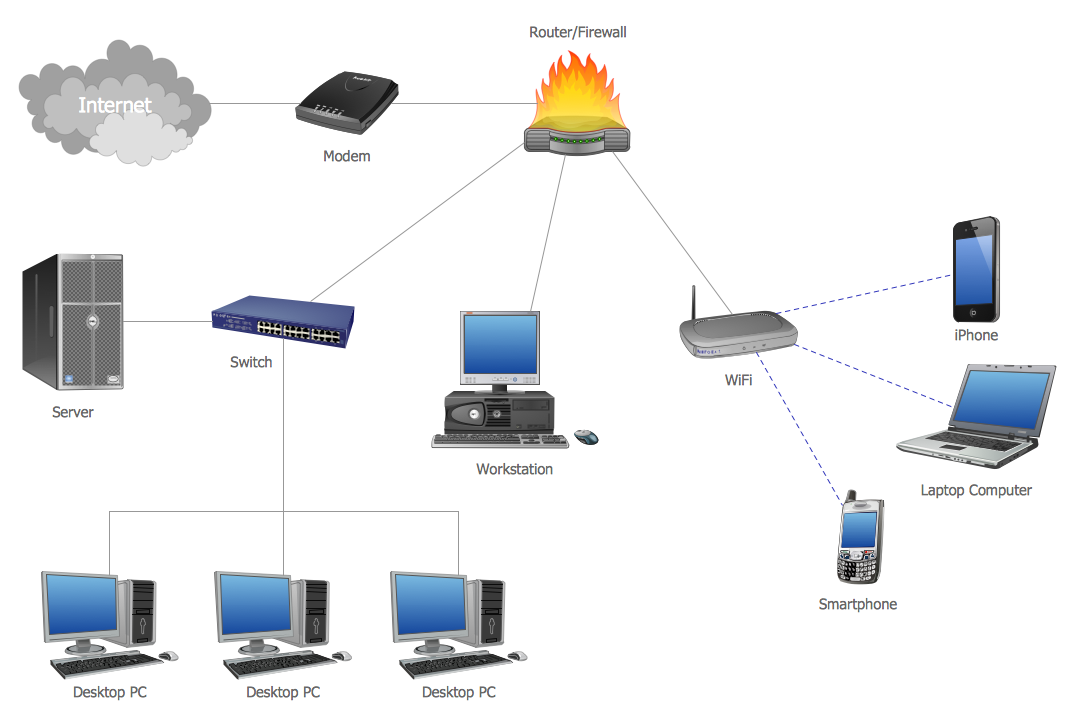

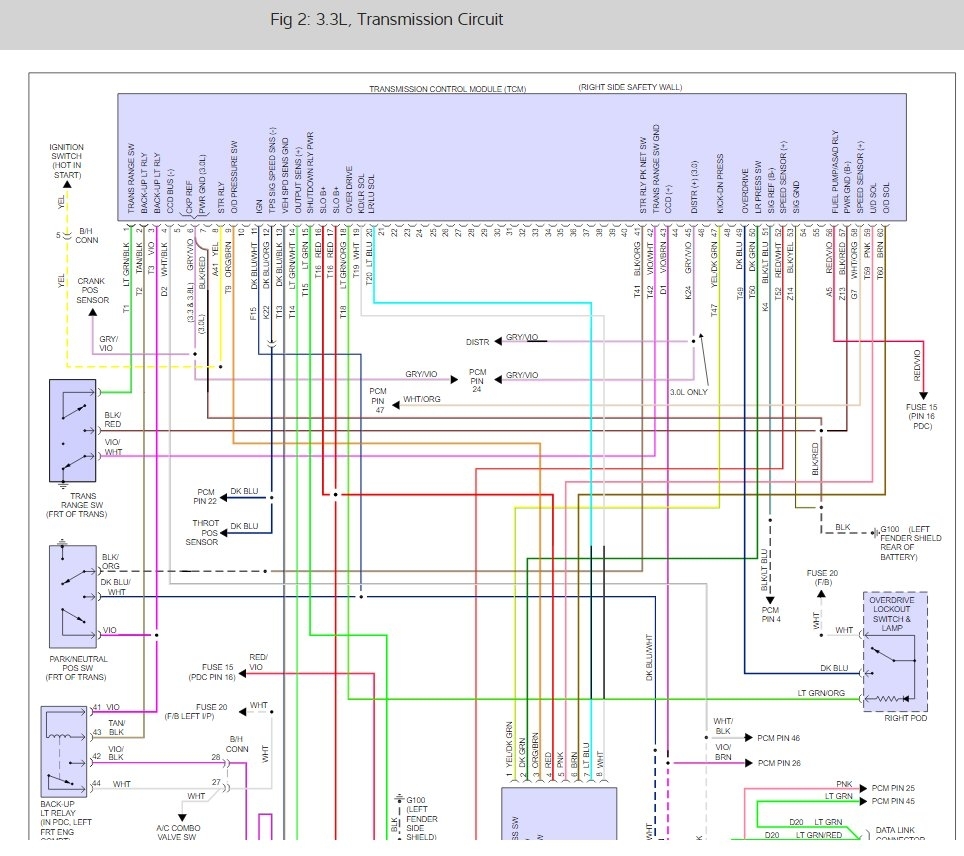

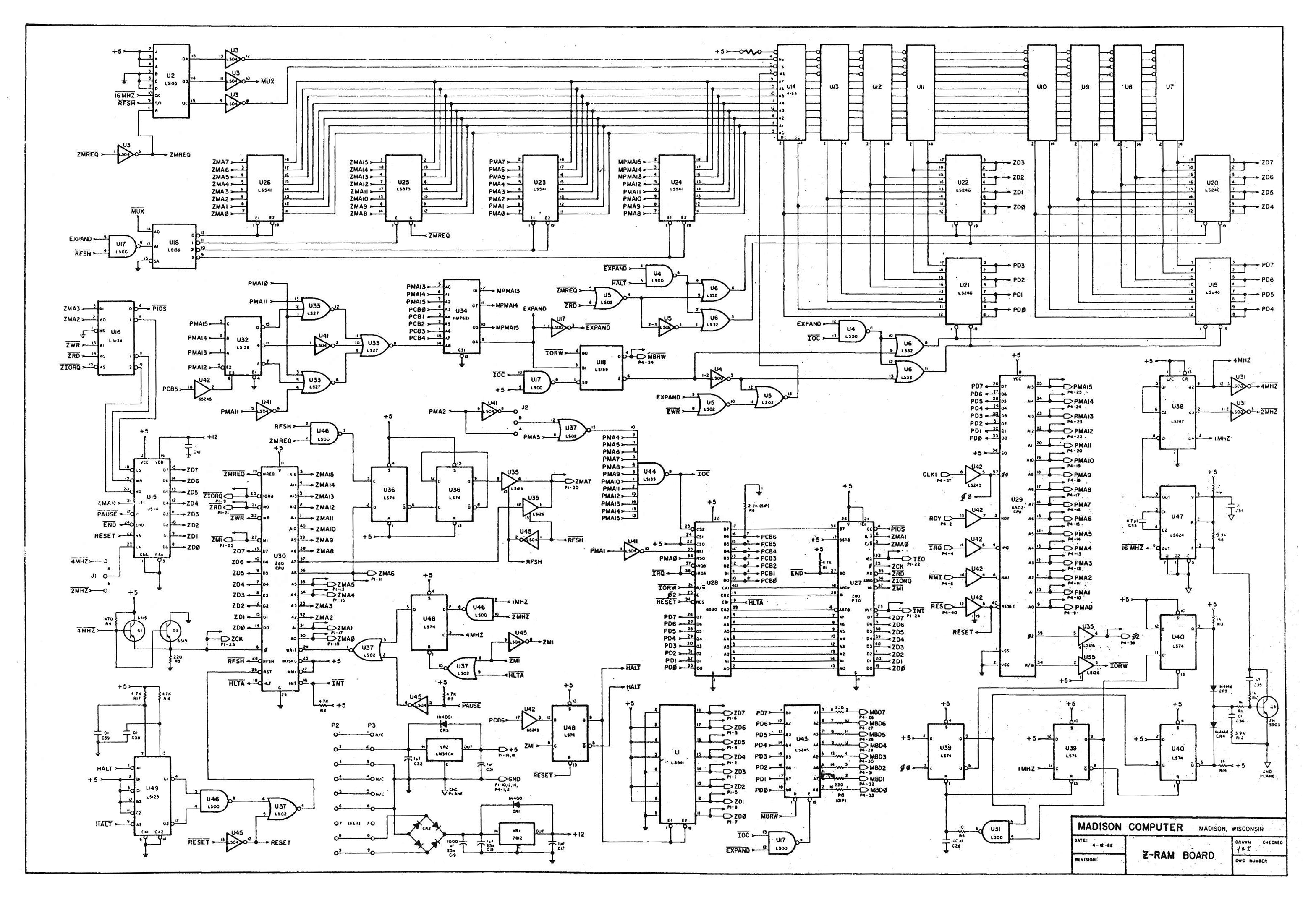

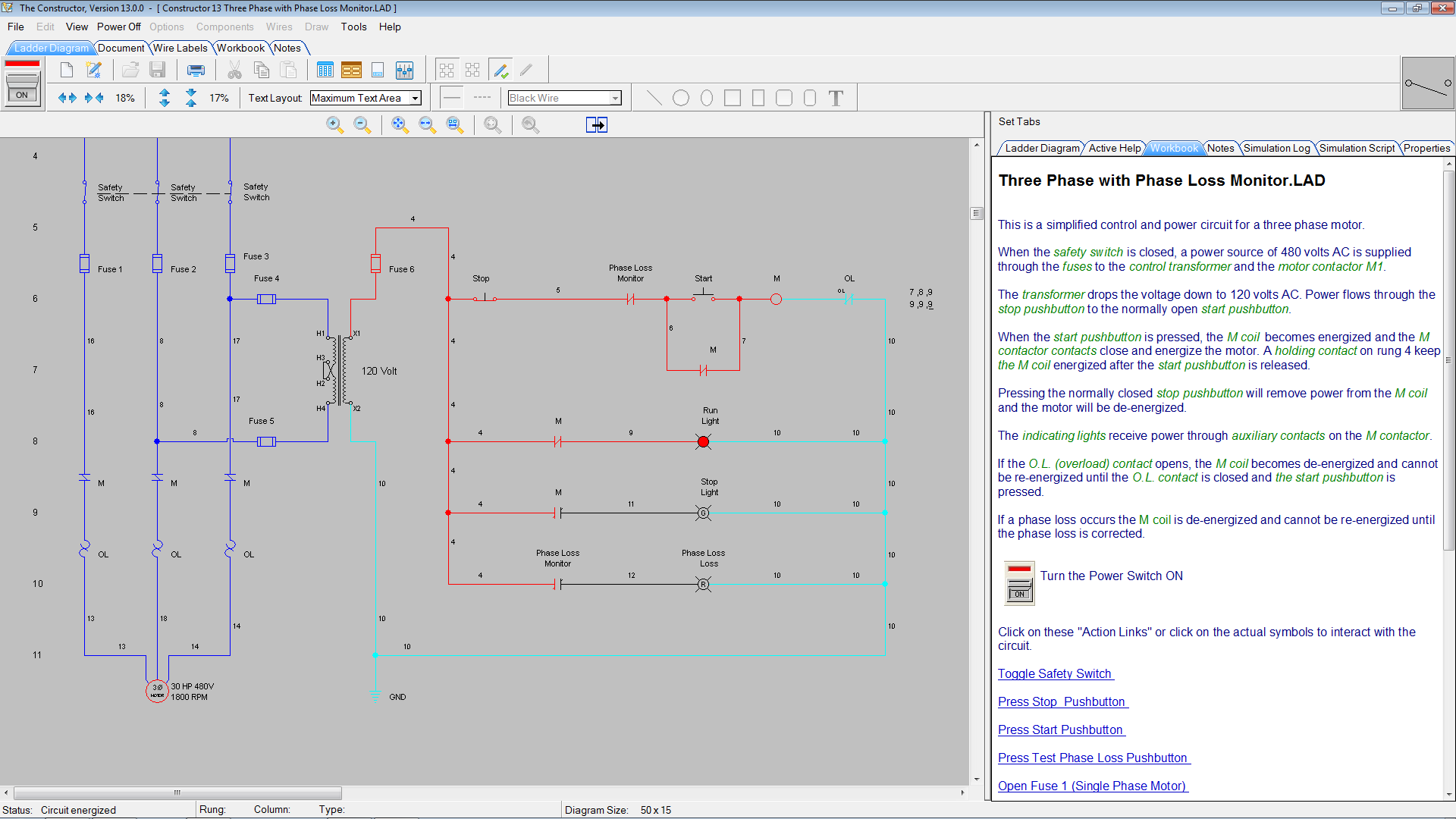

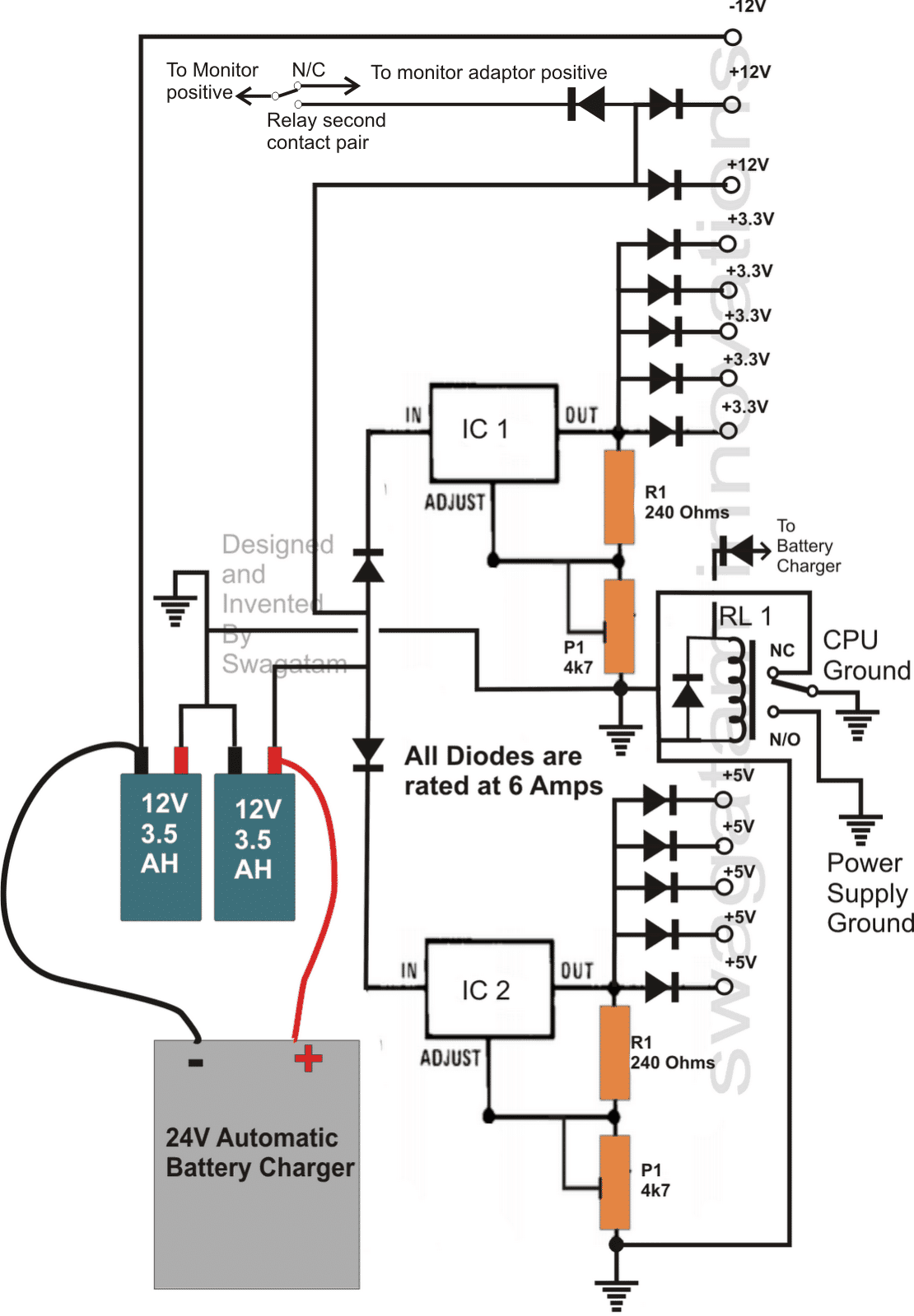

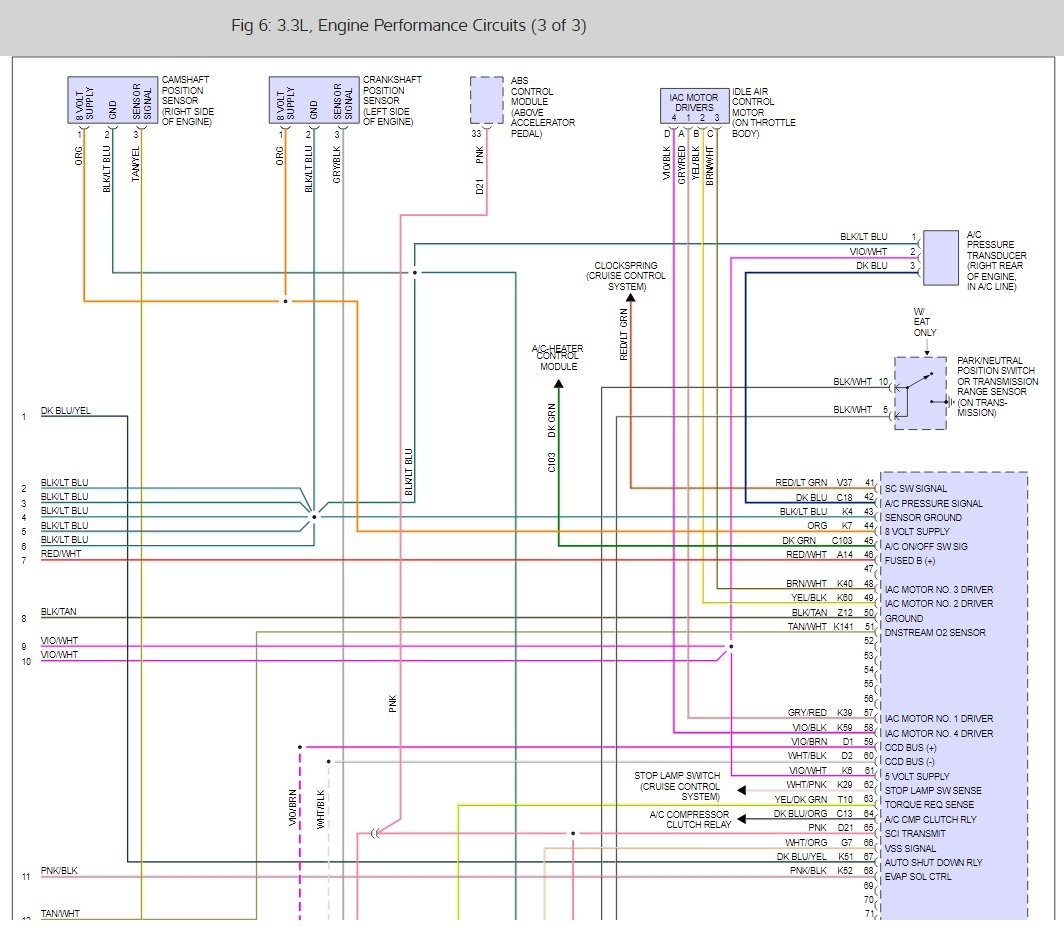

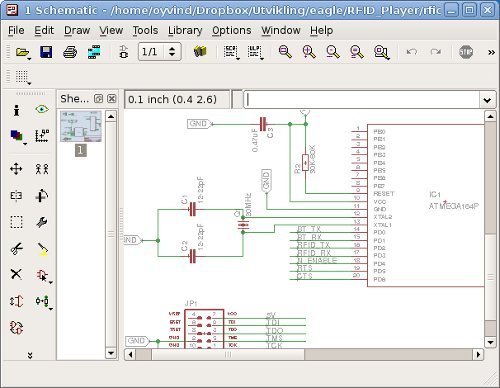

Documentation is the technical record of an electrical system. It includes schematics, wiring diagrams, terminal lists, load tables, and revisions that describe how each cable, breaker, and contact connects and functions. Engineers rely on these records to understand logic, verify safety, and maintain systems.

Accurate documentation begins at the design stage. Each circuit must have a distinct reference code that remains consistent between drawings and field labels. When changes occurrerouted cables, new junction boxes, or substitute partsthey must be reflected immediately in drawings. A mismatch between schematic and installation causes delays, confusion, and safety risks.

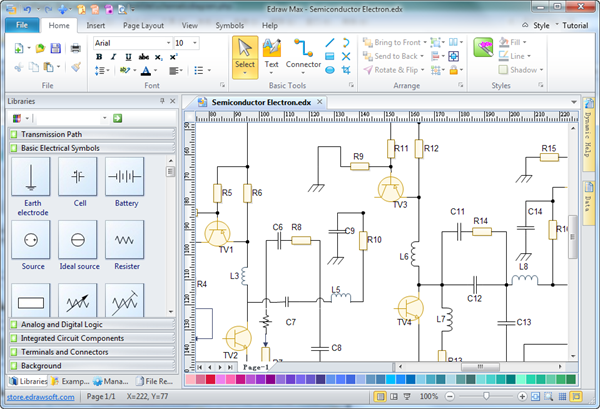

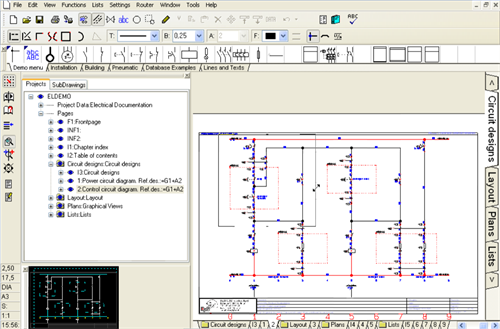

Modern tools like computer-aided electrical design systems generate uniform diagrams with linked parts data. Many integrate with maintenance databases, linking each component to equipment history and service reports.

### **Labeling and Identification**

Labeling turns documentation into visible reality. Every wire, terminal, and device should be clearly marked so technicians can work safely without guessing. Proper labeling reduces downtime and increases repair speed.

Effective labeling follows these principles:

- **Consistency:** Use one coherent coding method across entire installations.

- **Durability:** Labels must resist UV and mechanical wear. Heat-shrink sleeves, laser engraving, or metal tags last longer than paper or adhesive stickers.

- **Readability:** Font and color contrast should remain clear in dim environments.

- **Traceability:** Every label must correspond directly to schematics.

Color coding adds visual safety. standard IEC conductor colors remain common, while different colors separate control and power circuits.

### **Inspection and Verification**

Before energizing any system, conduct structured inspection and testing. Typical tests include:

- Line and neutral verification.

- Insulation-resistance measurements.

- Conductor resistance and protection checks.

- Simulation of interlocks and relays.

All results should be recorded in commissioning reports as baseline data for the assets lifecycle. Deviations found during tests must trigger corrective action and as-built updates.

### **Quality-Control Framework**

Quality control (QC) ensures build integrity from material to testing. It starts with verifying cables, terminals, and insulation ratings. Supervisors check torque, bend radius, and routing. Visual inspections detect damage, looseness, or contamination.

Organizations often follow international quality management systems. These frameworks require inspection reports, calibration records, and technician certifications. Digital QC systems now allow technicians to upload test data and photos. Managers can monitor progress remotely, reducing human error and paperwork.

### **Change Management and Revision Control**

Electrical systems rarely remain static. Components are replaced and extended over time. Without proper revision control, drawings quickly become outdated. Each modification should include a revision number, author, and date. As-built drawings must always reflect the final installed condition.

Version control tools track modifications centrally. This prevents duplicate work and data loss. Historical logs allow engineers to trace failures to their origin.

### **Training and Organizational Culture**

Even the best systems fail without disciplined people. Teams must treat documentation as a professional responsibility. Each recorded detail contributes to long-term reliability.

Training programs should teach labeling standards, documentation tools, and QC procedures. Regular audits help reinforce habits. routine field reviews confirm that labeling matches diagrams. Over time, this builds a workforce that values detail and consistency.

Ultimately, documentation is not bureaucracyits engineering memory. A system that is organized, traceable, and continuously updated remains reliable, maintainable, and future-ready. When records stay current, electrical systems stay dependable for decades.