Todays electrical infrastructures depend on sophisticated methods of energy management and safety that go far beyond simple wires and fuses. As demands grow, so do the standards for precision, safety, and efficiency in delivering electrical energy to every load. From automotive and aerospace, understanding modern power-control logic is crucial for designing and maintaining resilient electrical networks under all conditions.

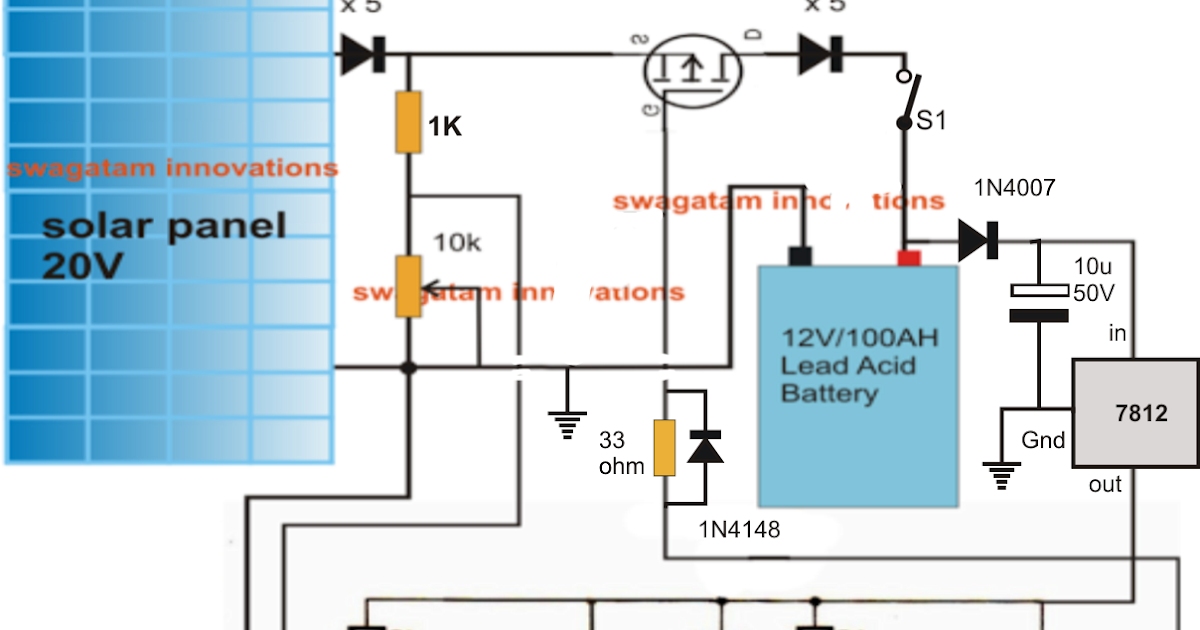

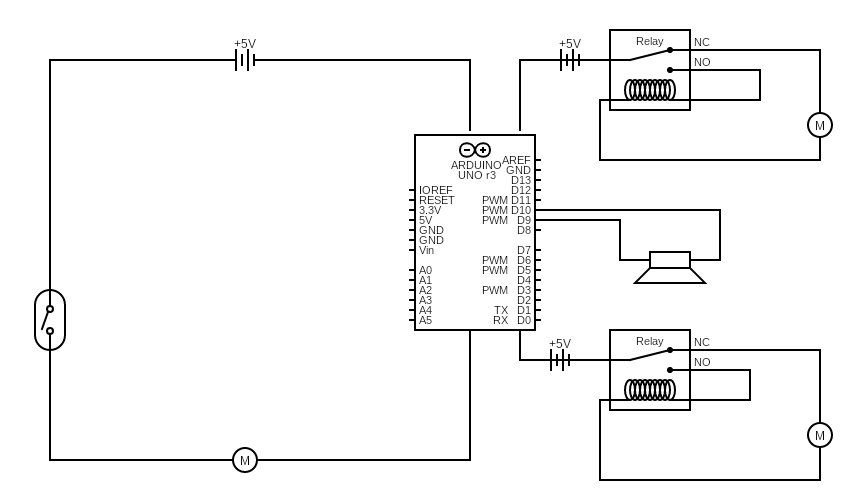

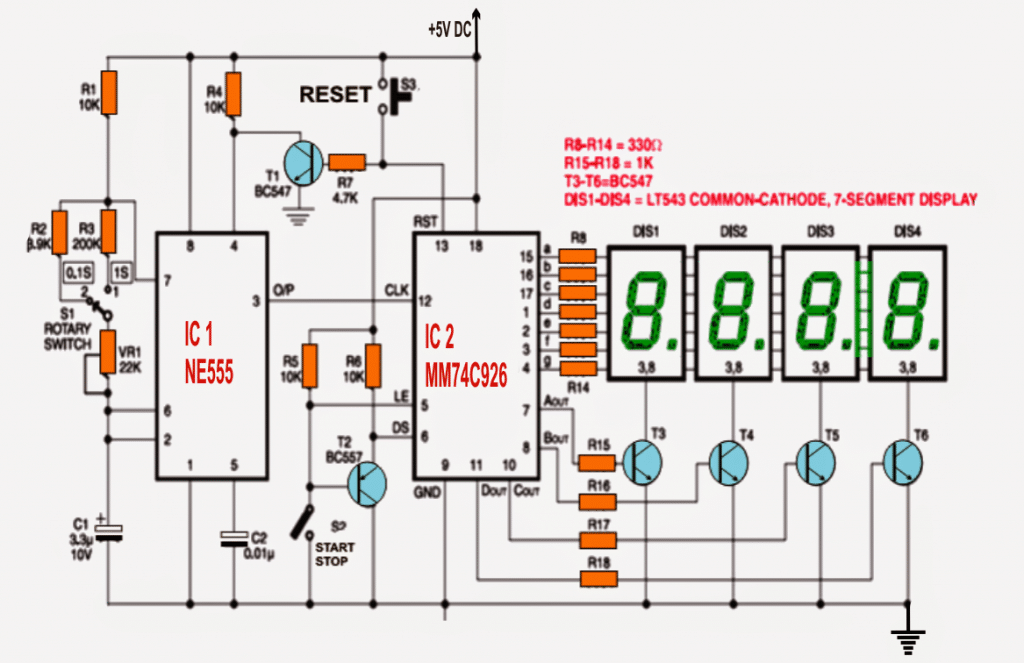

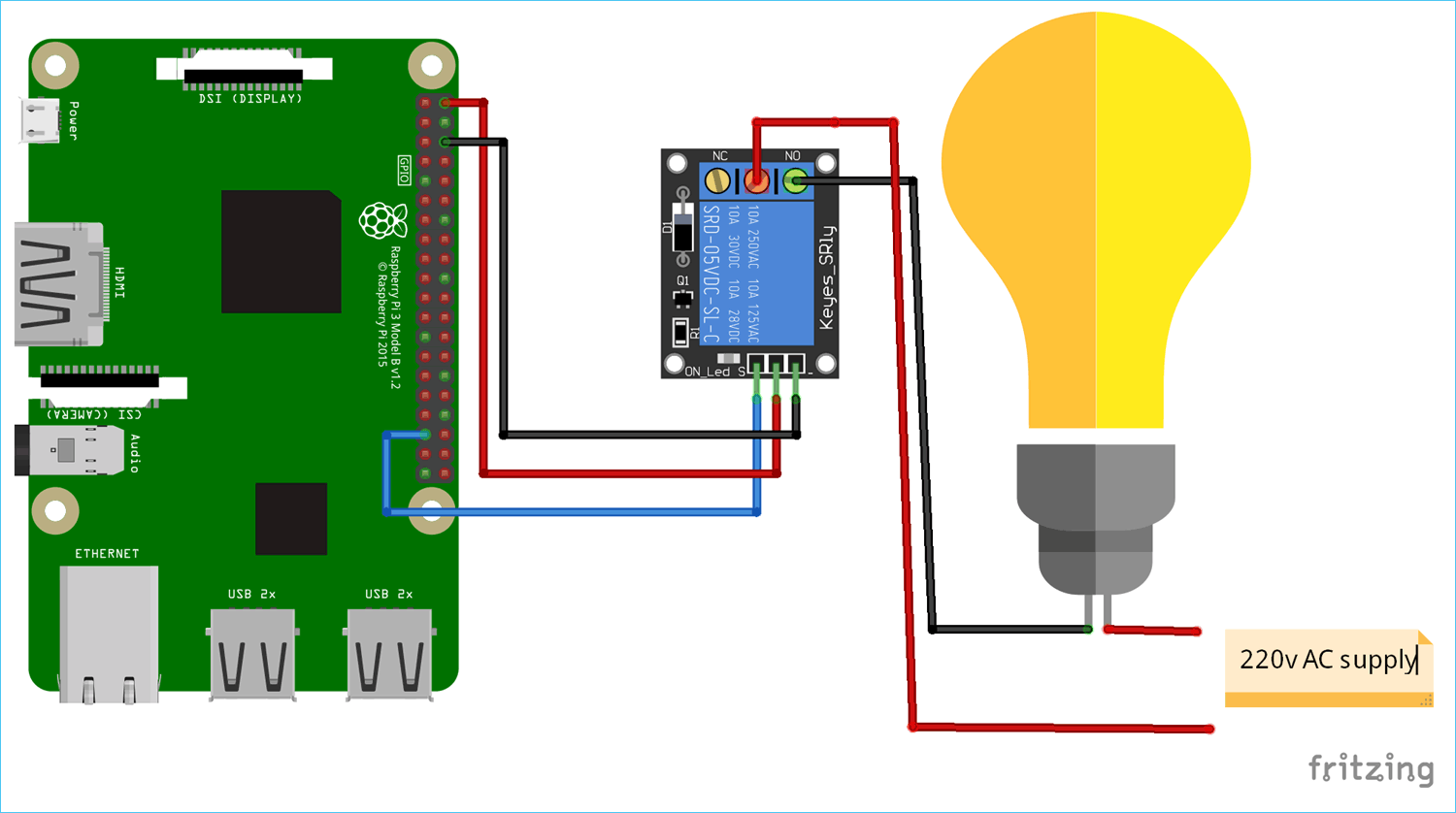

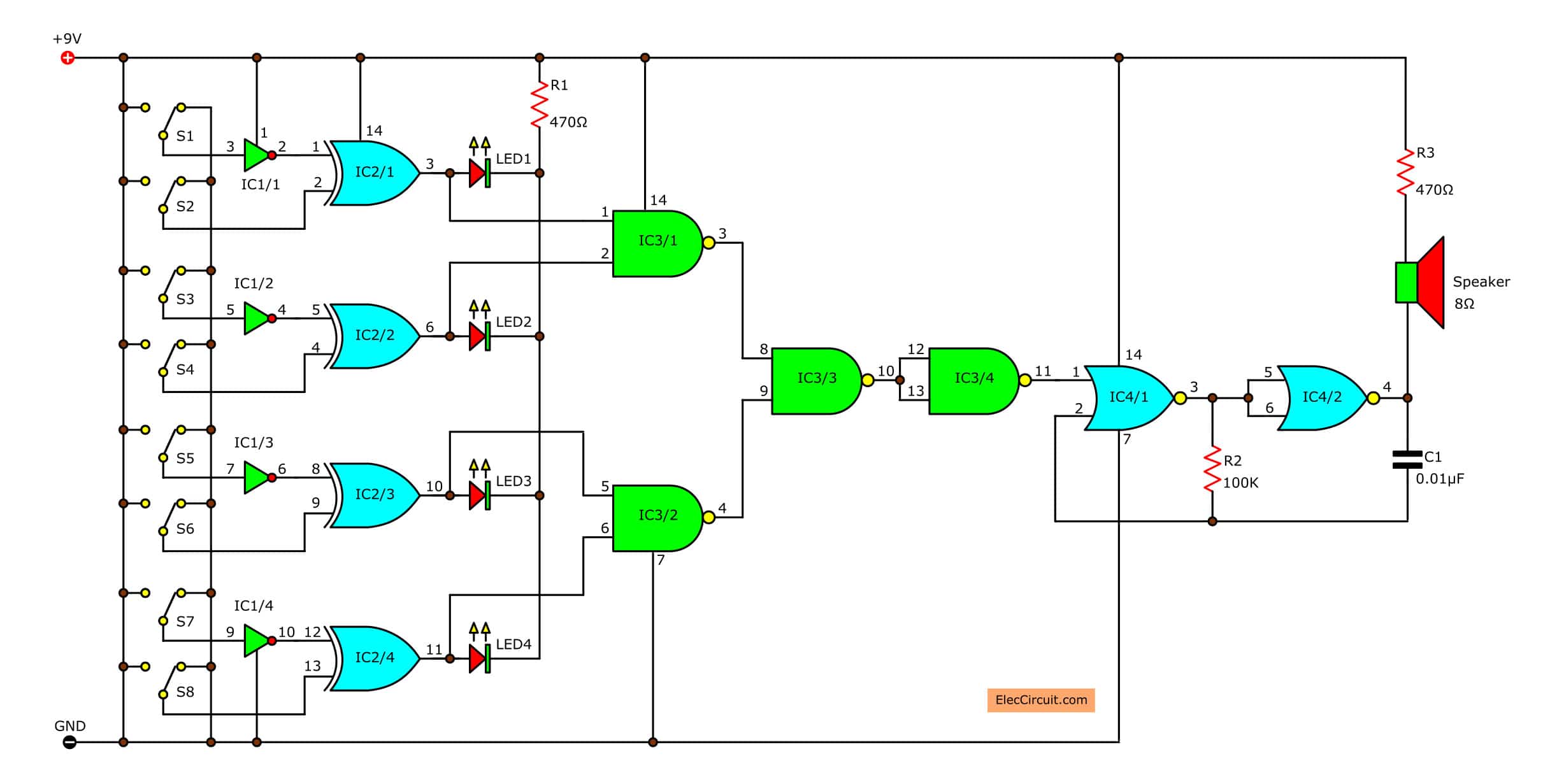

At its foundation, power distribution is the process of transmitting power from a single source to multiple destinations without voltage drop or instability. Traditional systems relied on mechanical relays, switches, and fixed fuses to manage power. While reliable for decades, these methods struggle when facing dynamic modern loads. To meet new operational standards, engineers now employ intelligent fuse networks, e-fuses and control logic, and real-time monitoring circuits that respond instantly to load variations.

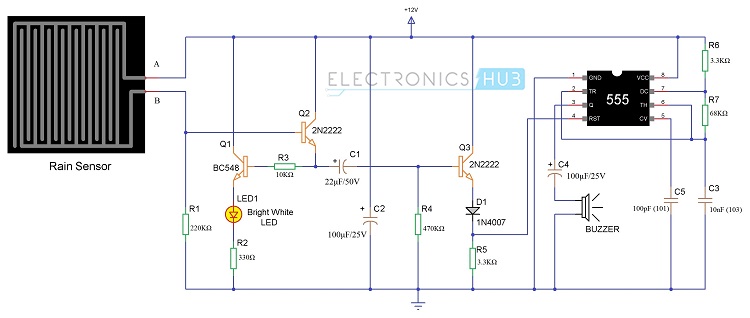

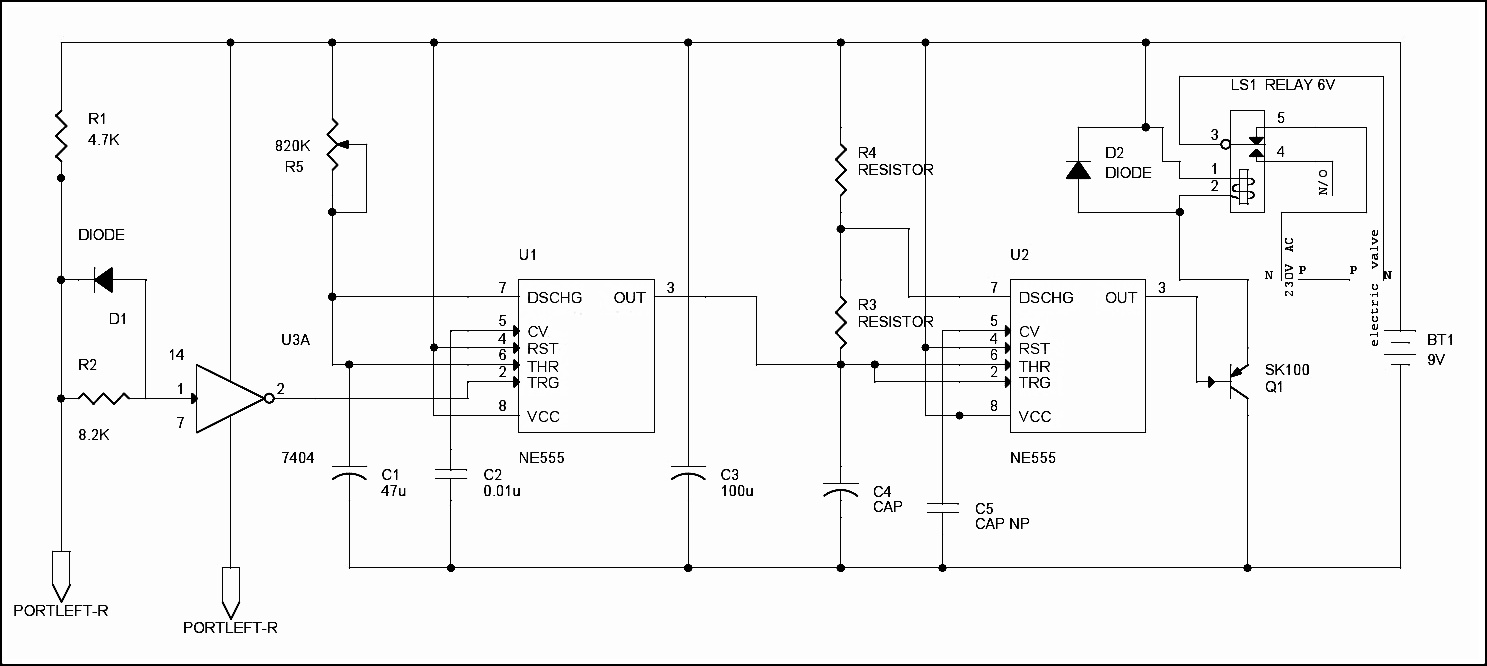

An digital fuse performs the same function as a conventional one but with precision control. Instead of melting metal, it detects and isolates faults electronically, often within microseconds. Many e-fuses reconnect after the fault clears, eliminating manual replacement. Advanced versions also communicate diagnostics via industrial communication buses, sharing status and fault history for deeper insight.

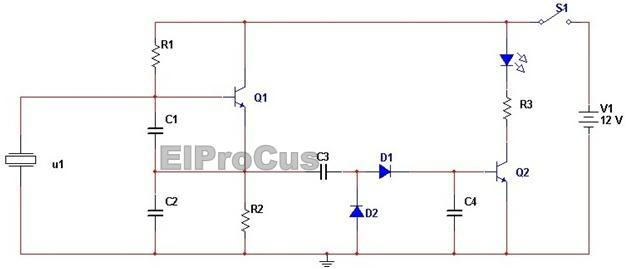

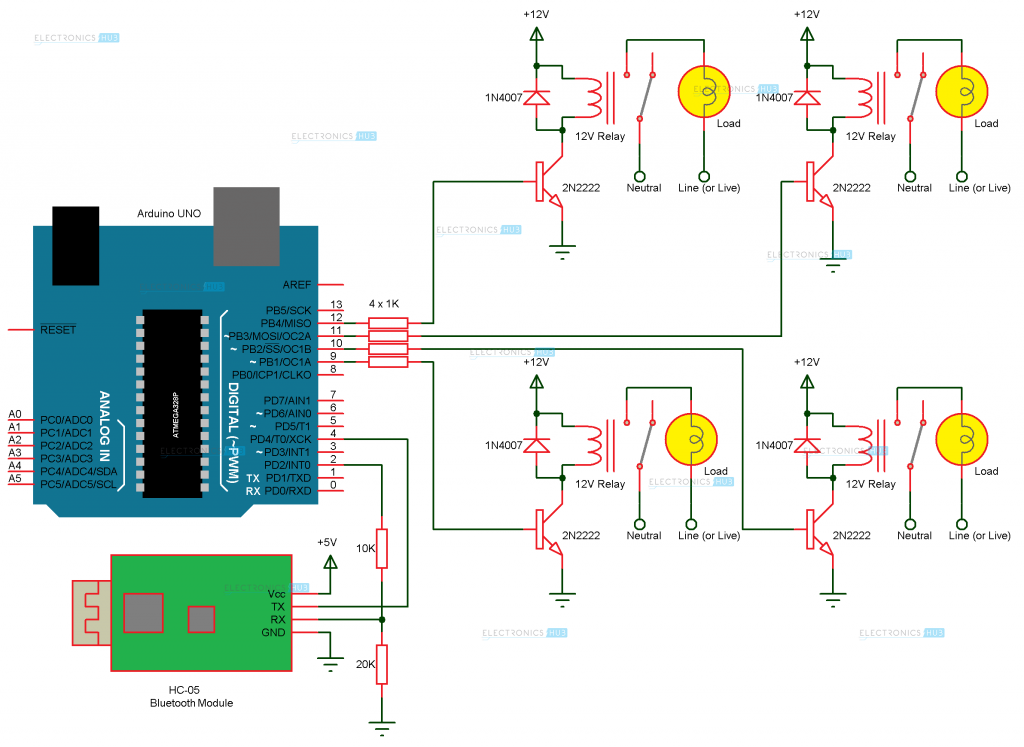

MOSFET switches have replaced mechanical contactors in many industrial and vehicular applications. They switch faster, create less electrical noise, and suffer no mechanical wear. In environments subject to shock and harsh conditions, solid-state components outperform mechanical types. However, they introduce thermal challenges, since semiconductors generate heat under heavy load. Engineers mitigate this through careful design and cooling integration.

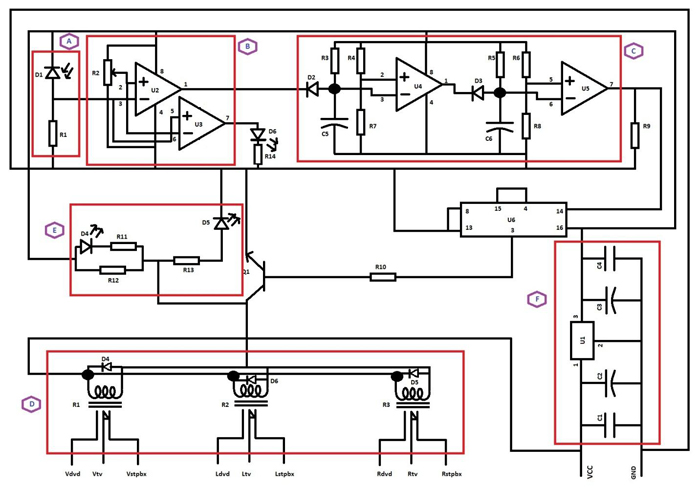

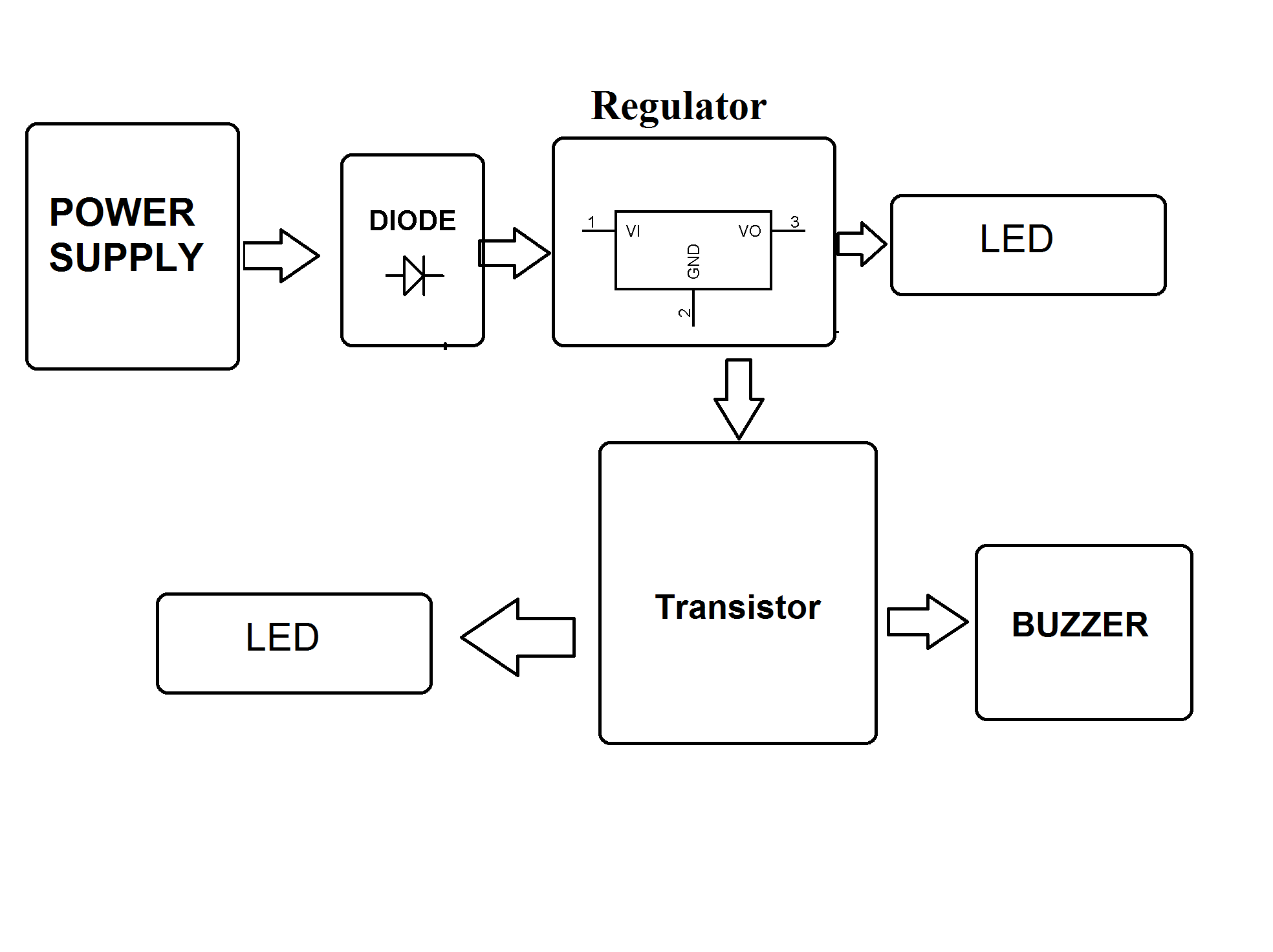

A well-structured power distribution architecture separates main, auxiliary, and control subsystems. Main feeders use copper rails and conductors, branching into localized subnets protected by local fuses or limiters. Each node balances between safety and uptime: too tolerant and faults persist; too strict, and false trips occur. Smart systems use adaptive thresholds that distinguish temporary surges from actual faults.

Grounding and return-path design form the invisible backbone of modern power networks. Multiple groundssignal, power, and chassismust remain isolated yet balanced. Poor grounding causes offsets, EMI, or data corruption. To prevent this, engineers implement star or single-point grounding, using low-impedance connections that maintain stability under vibration. Control units and sensors now monitor ground integrity in real time to detect early degradation or corrosion.

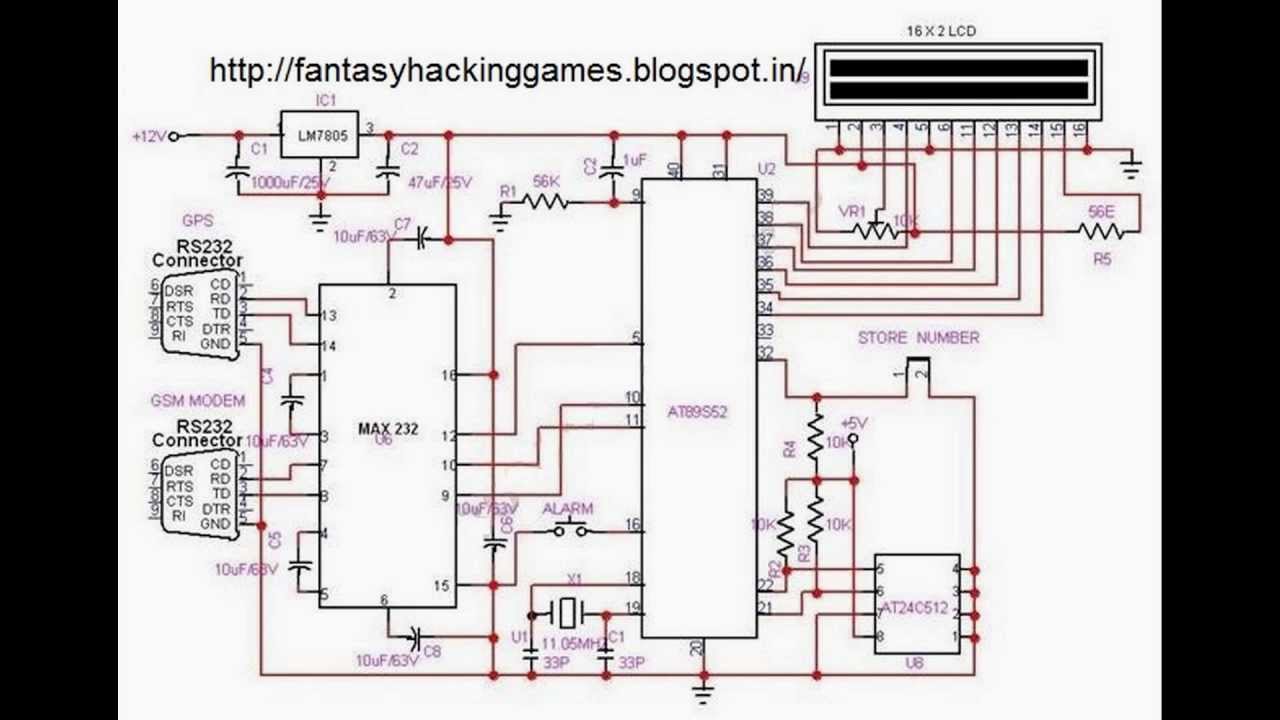

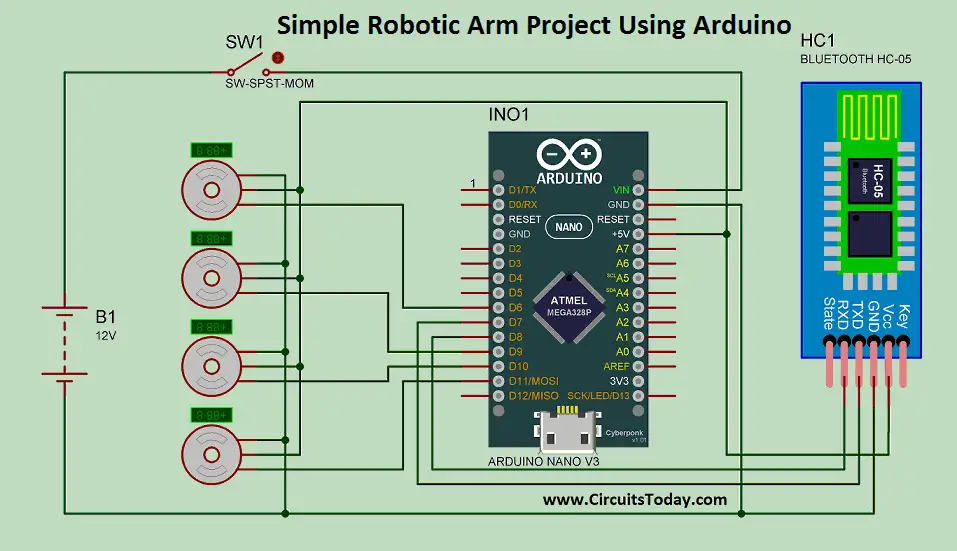

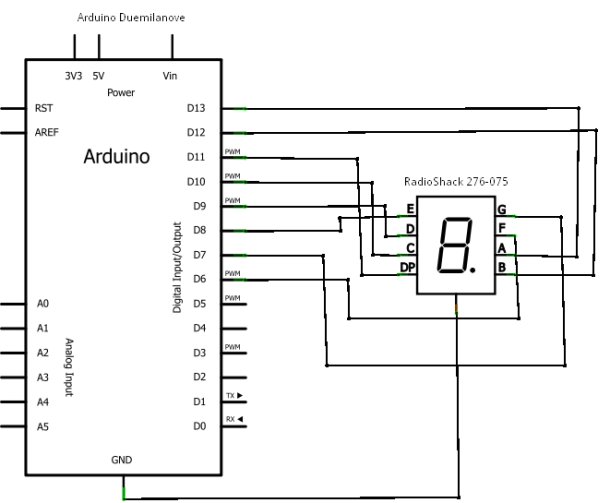

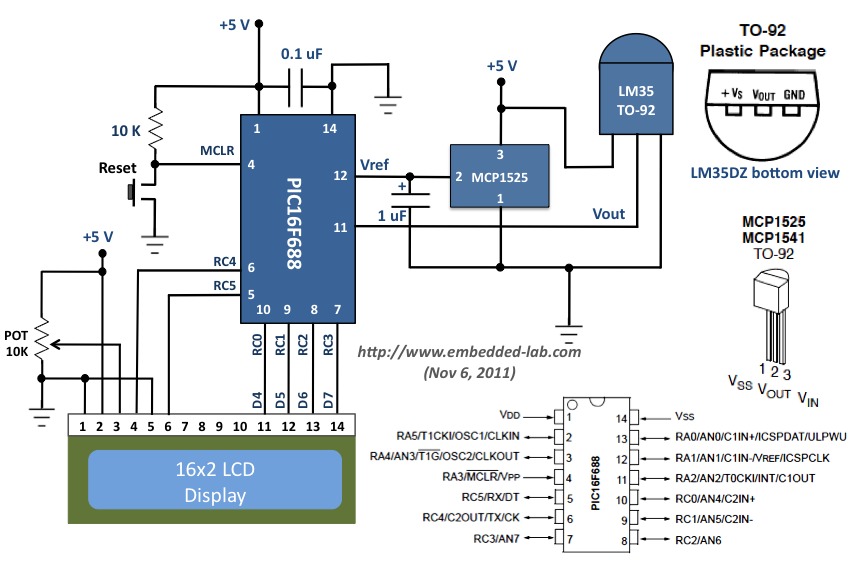

The fusion of electronics and power systems marks a major shift in energy control. Microcontrollers within PDMs and switchboards measure real-time loads, log data, and coordinate switching. This intelligence enables data-driven reliability, where systems alert operators before breakdowns. Supervisory software visualizes current paths, fuse status, and system health across entire installations.

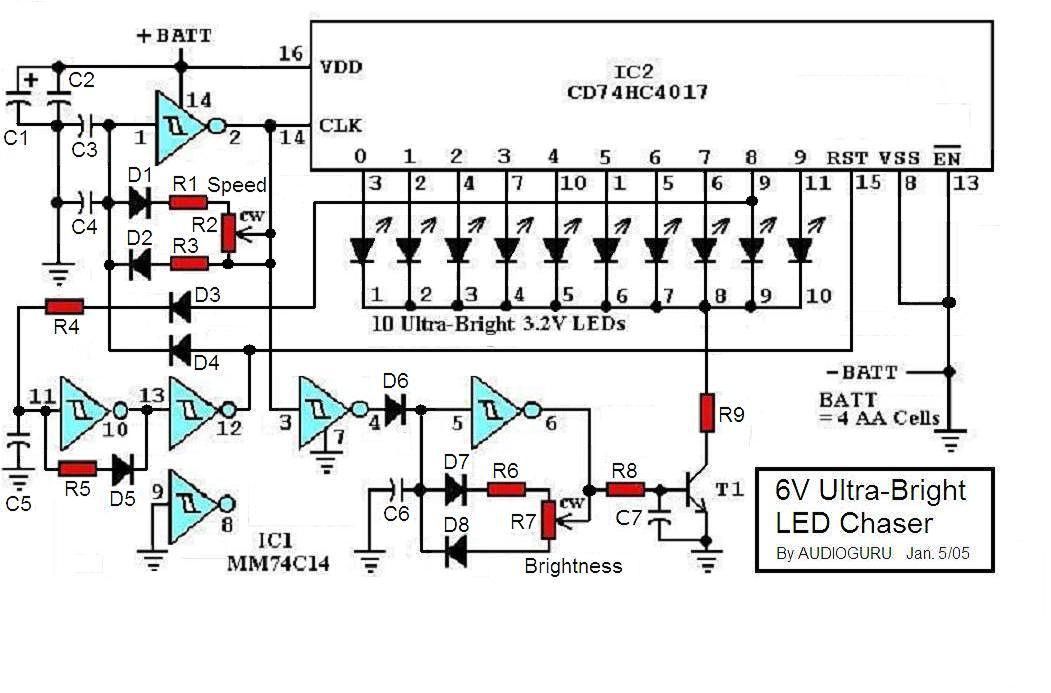

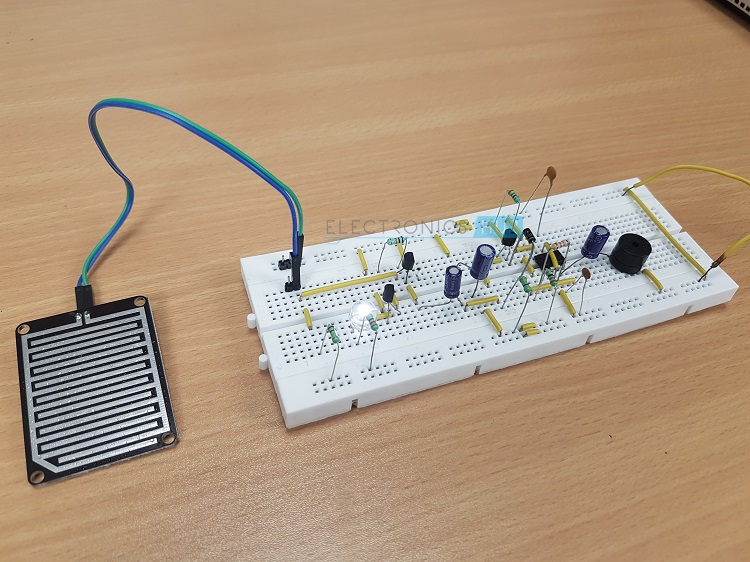

Protection components themselves have evolved. In addition to e-fuses, engineers employ polyfuses (PTC resettable fuses) and magnetic-trip protection. Polyfuses increase resistance as they heat, resetting automatically after coolingideal for low-voltage or compact circuits. Current-limiting breakers trip fast enough to cap energy before conductors overheat. Selection depends on load type and criticality.

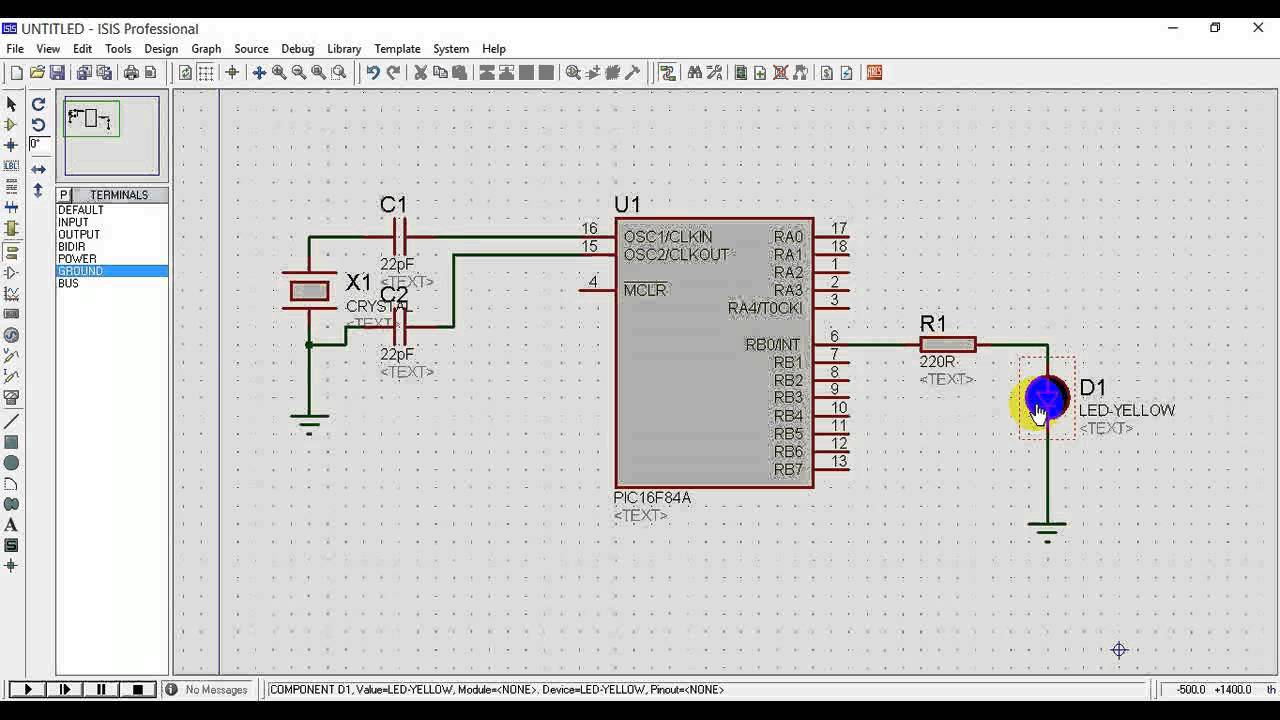

Modern simulation tools enable engineers to model faults and heat flow before hardware is built. By analyzing voltage drop, conductor temperature, and fuse response, they ensure cables operate within ampacity limits. These digital models lead to predictable, safe systems.

From a maintenance view, smart distribution simplifies troubleshooting and monitoring. Built-in sensors and logs record overcurrent events, pinpoint fault locations, and allow remote resets via software. This is invaluable in hard-to-reach installations, reducing service time and cost.

Despite new technologies, the principles remain timeless: electricity must flow efficiently, safely, and controllably. Whether through copper conductors or silicon switches, each design must protect the circuit, contain failures fast, and maintain traceable schematics.

In the broader engineering context, advanced distribution and modern fusing techniques represent the future of electrical safety. They show how hardware and firmware now combine to form adaptive systems that are not only secure but also self-aware and self-correcting. Through these innovations, engineers balance reliability with intelligence, ensuring that energy continues to power the world with precision.