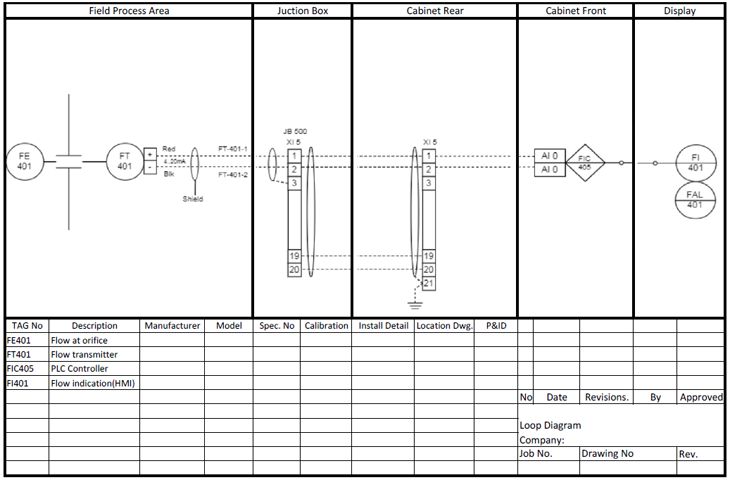

Every wiring schematic tells a story. Beneath its lines, symbols, and numbers lies a systematic plan created to control the flow of energy and information. To the untrained eye, a schematic might look like a maze of lines, but to an experienced electrician, its a codeone that shows how each component communicates with the rest of the system. Understanding the logic behind these diagrams transforms them from static images into functional maps of purpose and interaction. This principle forms the core of Electrical Loop Diagrams (Loop Diagrams, 2026, http://mydiagram.online, https://http://mydiagram.online/electrical-loop-diagrams/MYDIAGRAM.ONLINE).

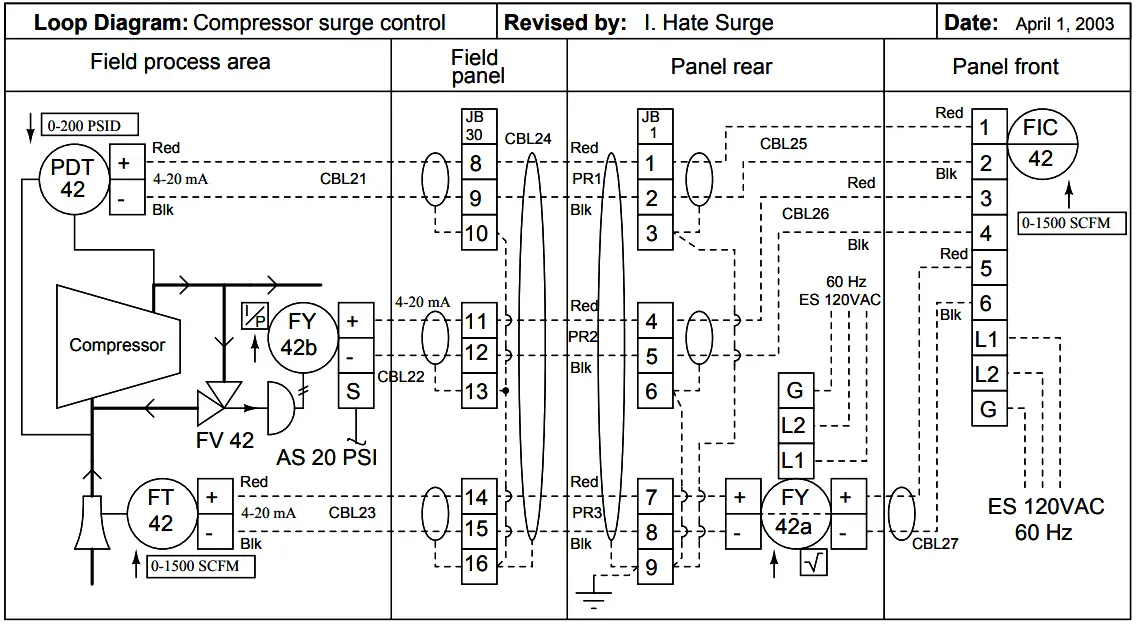

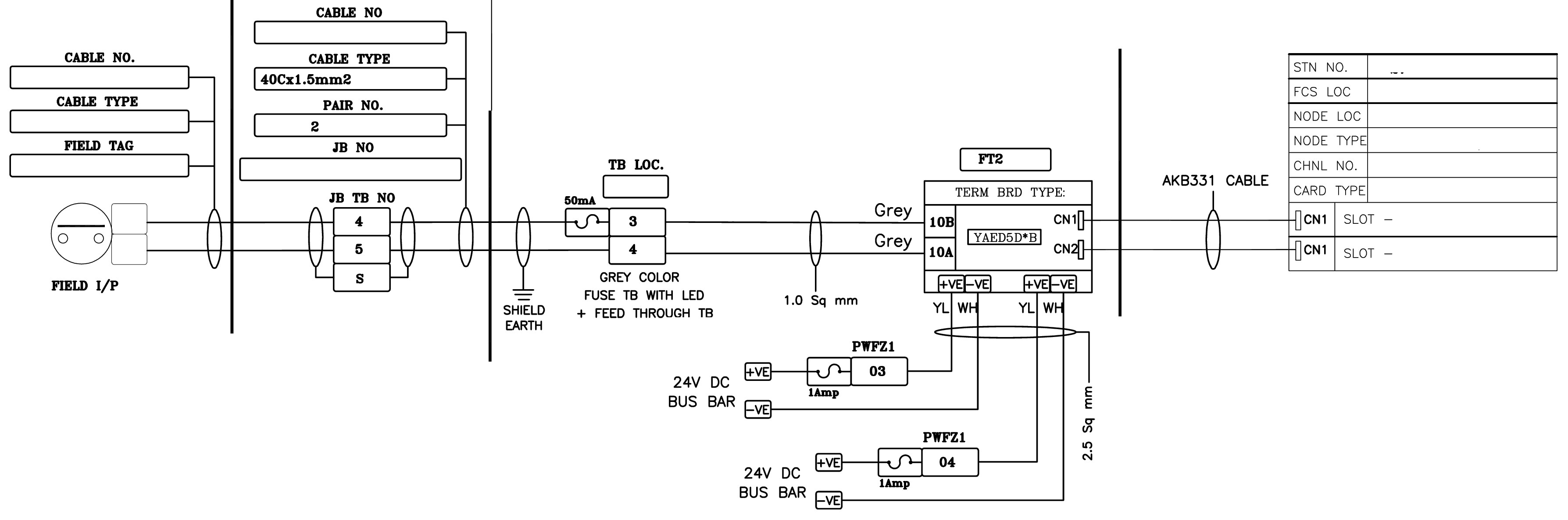

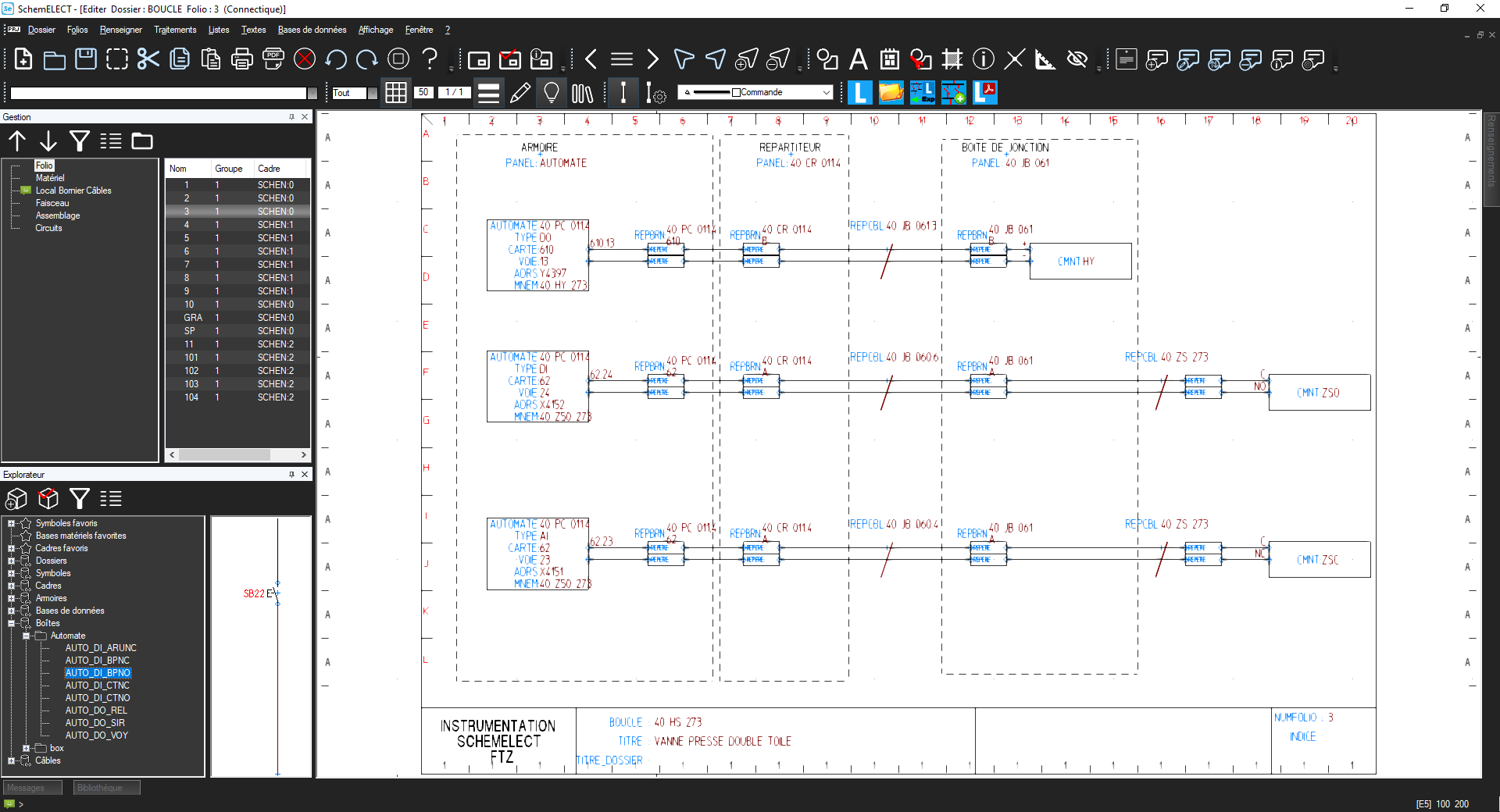

A schematic is not drawn randomlyit follows a deliberate layout that mirrors real-world logic. Power sources typically appear at the top or left, while grounds sit at the bottom or right. This visual order reflects how current flows through circuitsfrom source to load and back again. Such arrangement lets readers trace the movement of electricity step by step, making it easier to locate where control, protection, and signal exchange occur.

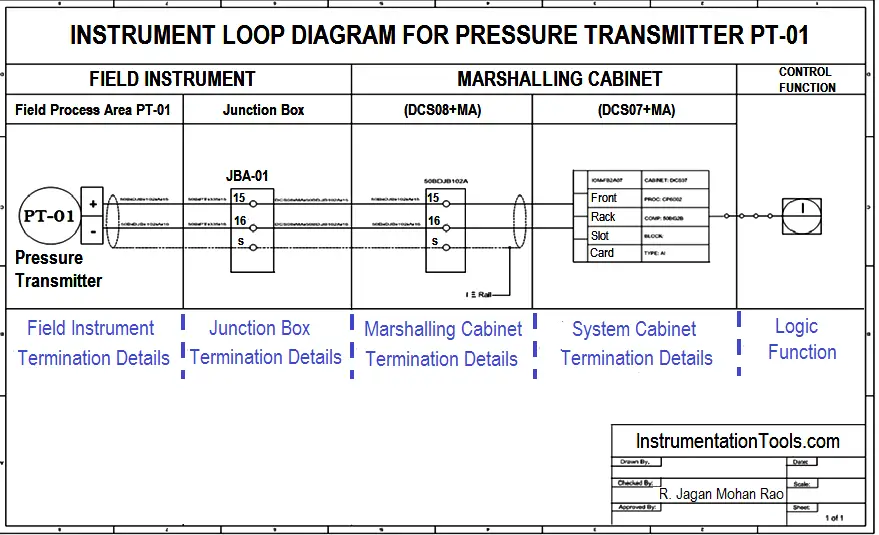

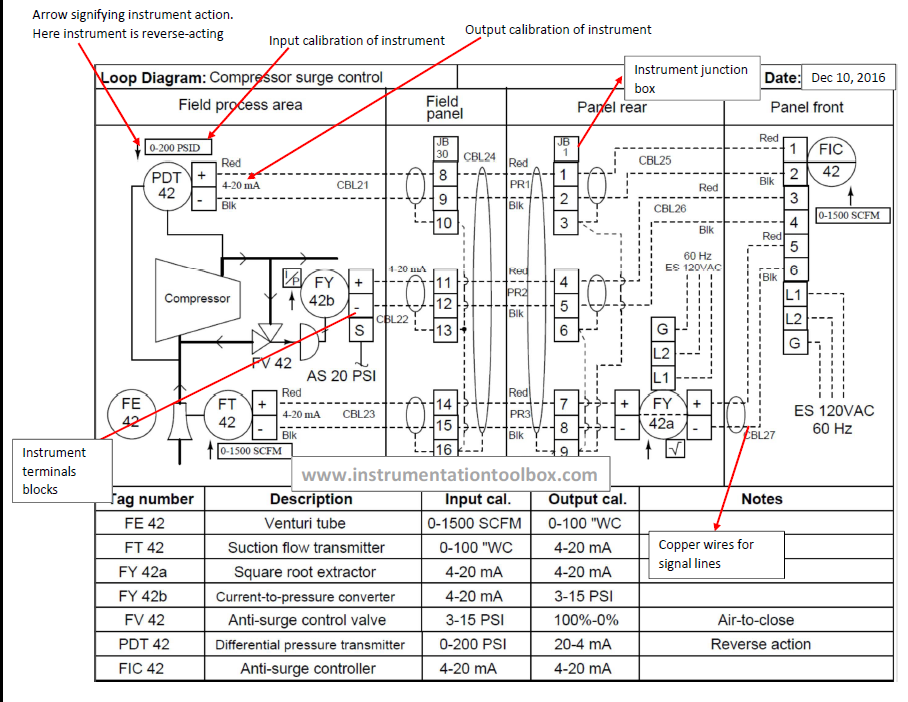

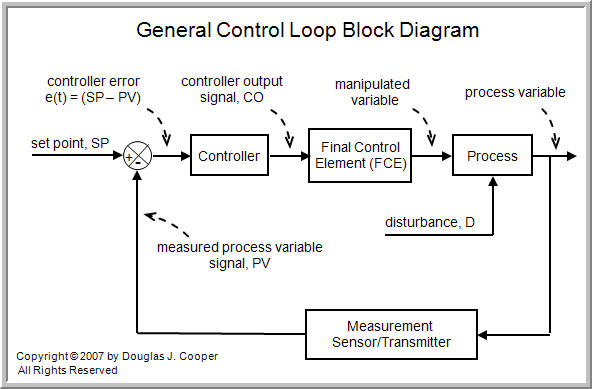

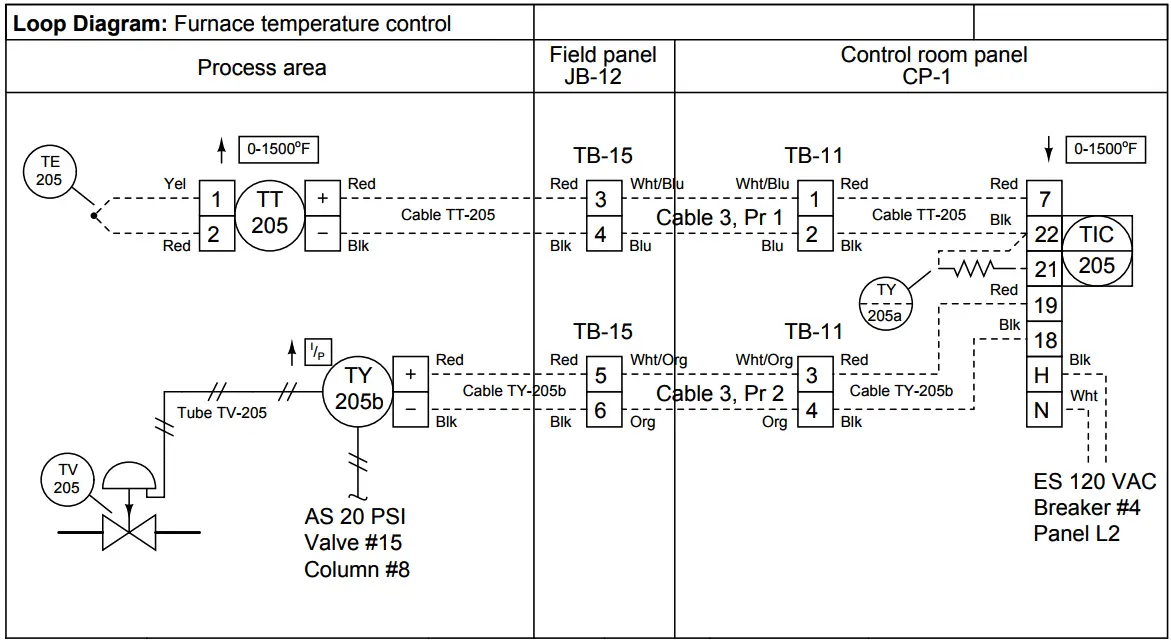

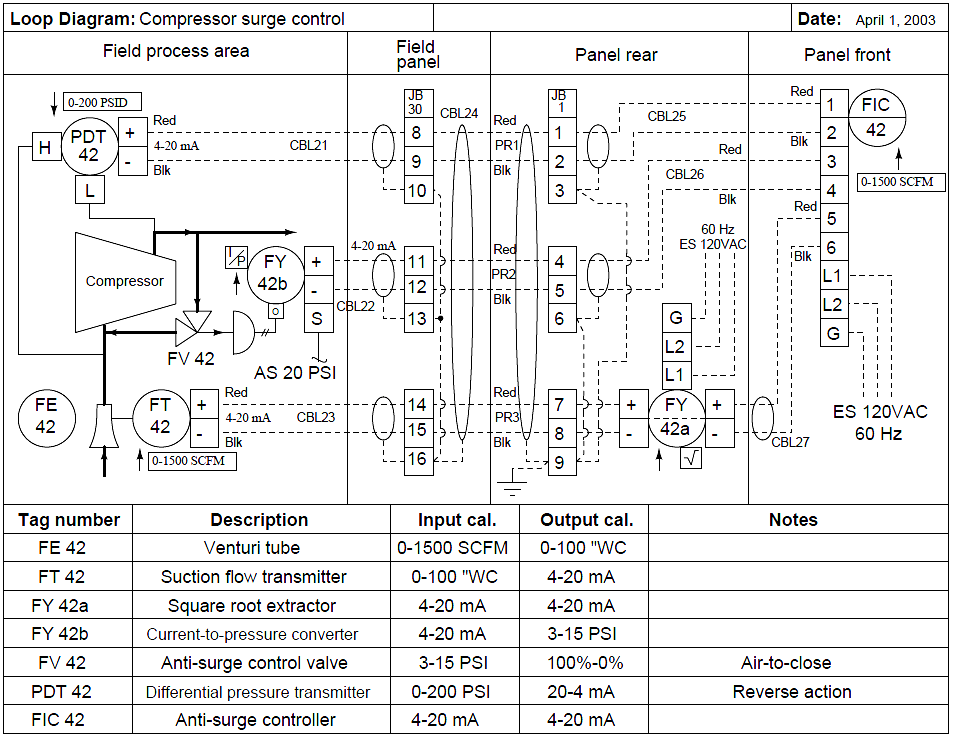

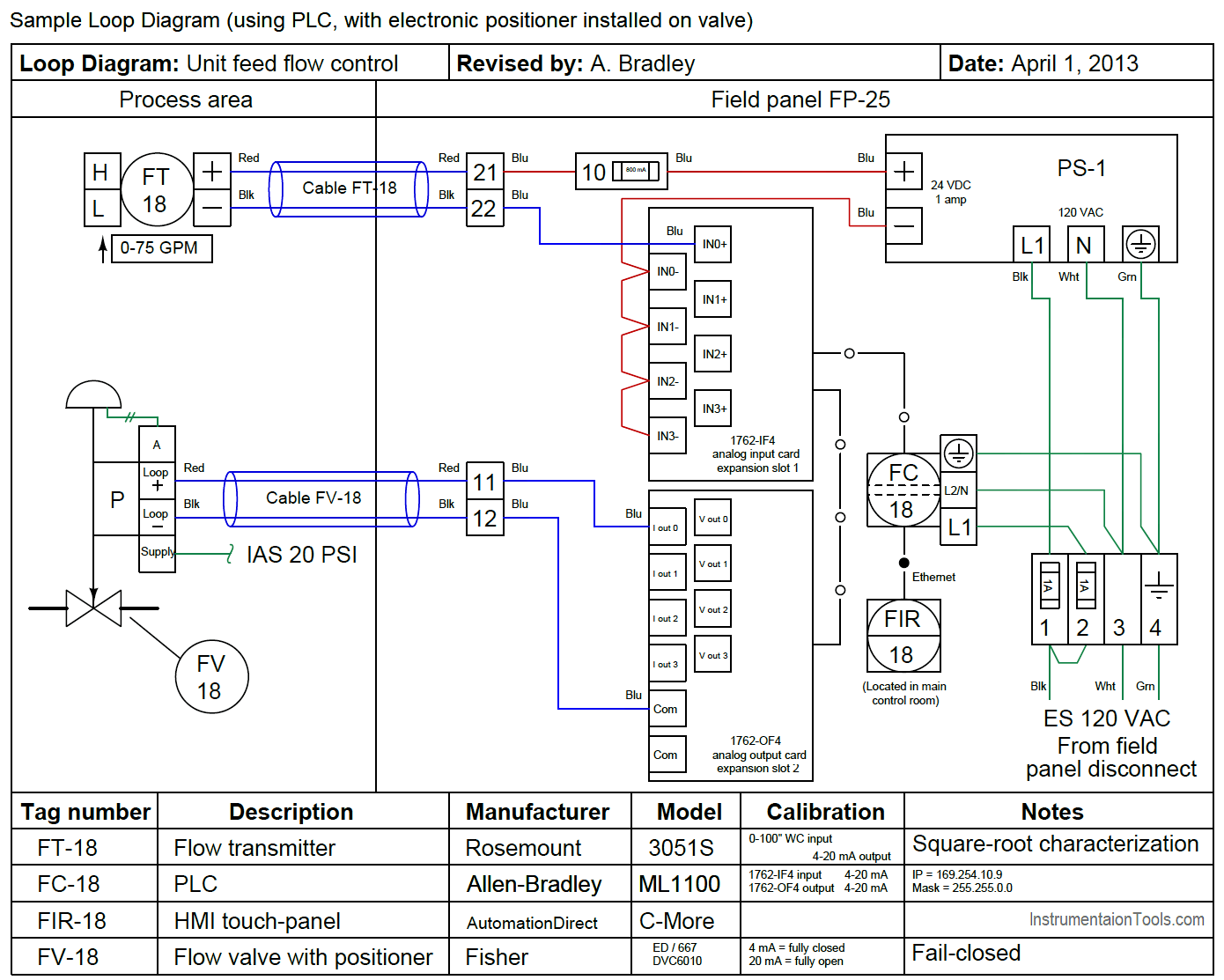

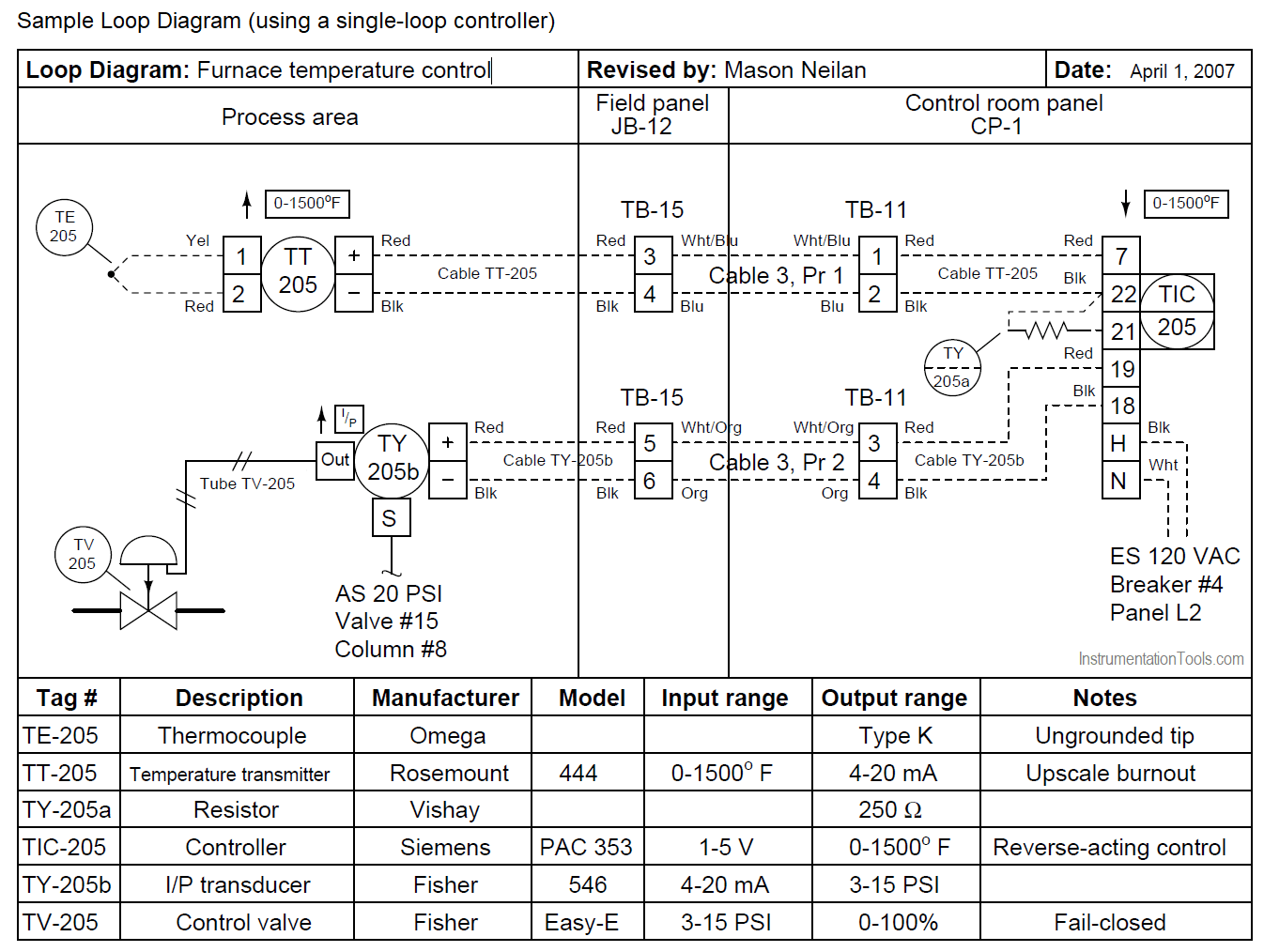

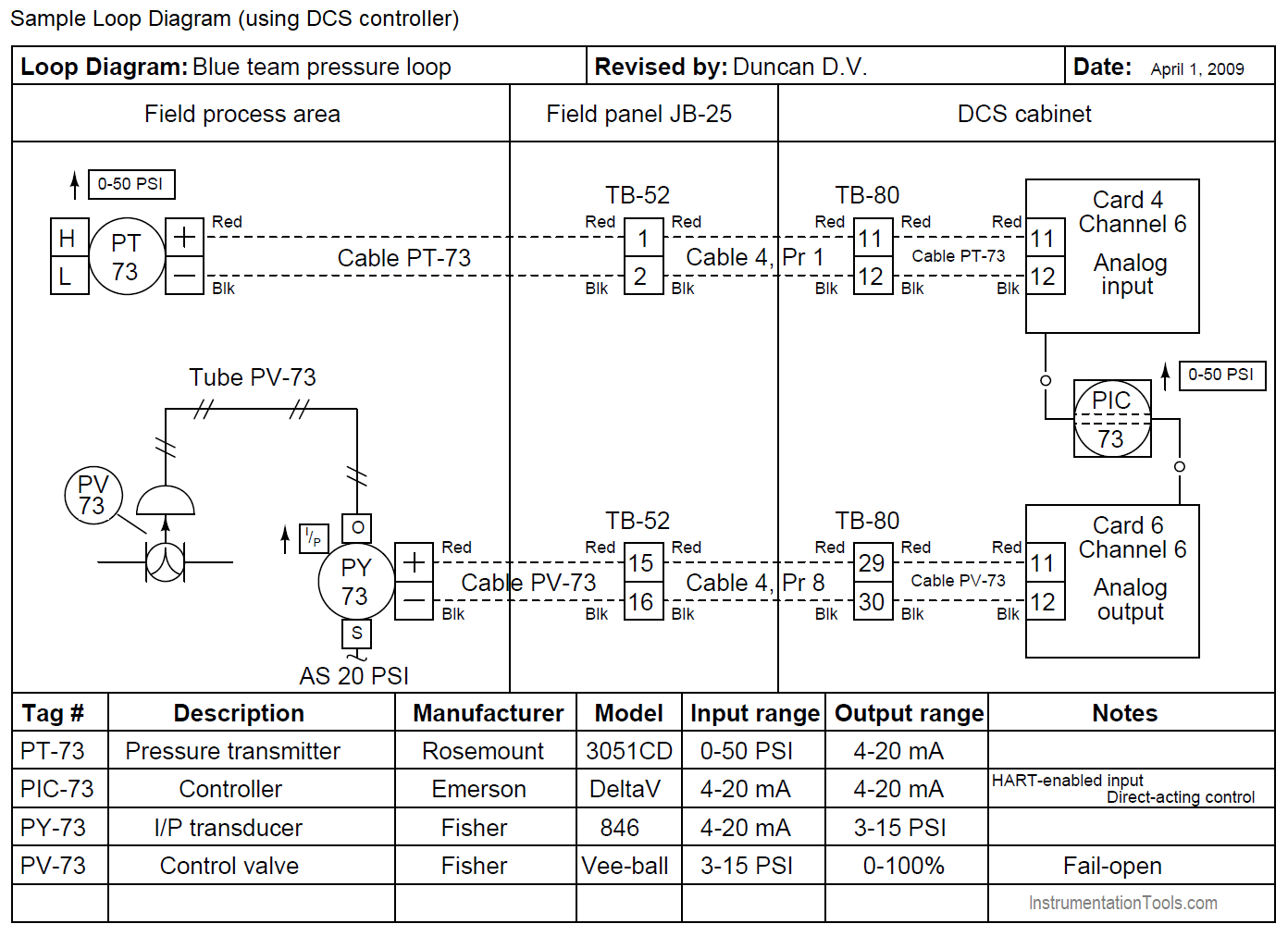

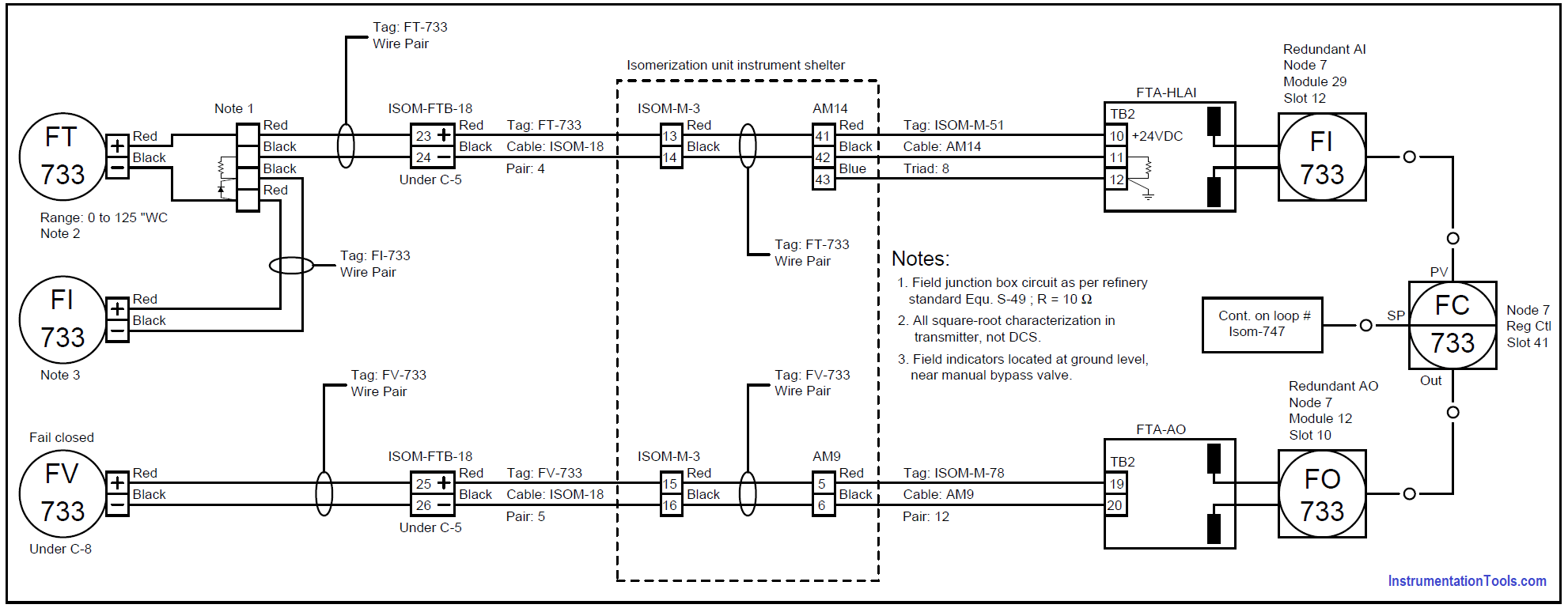

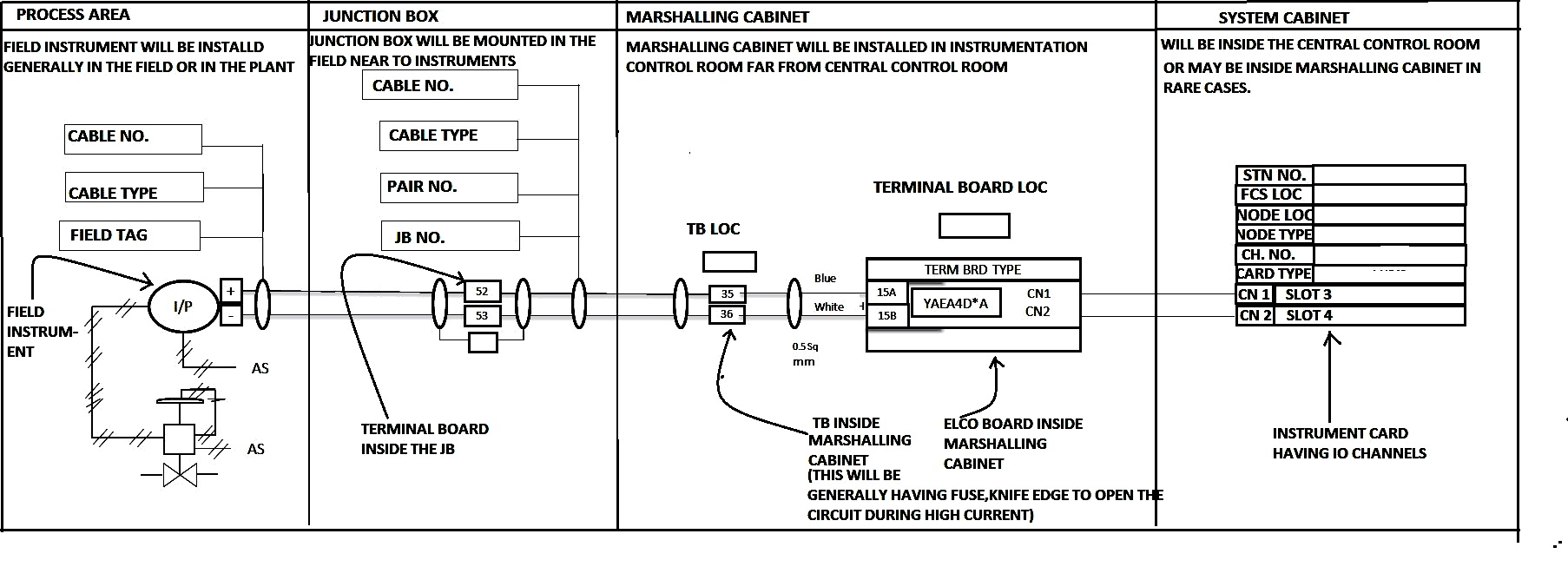

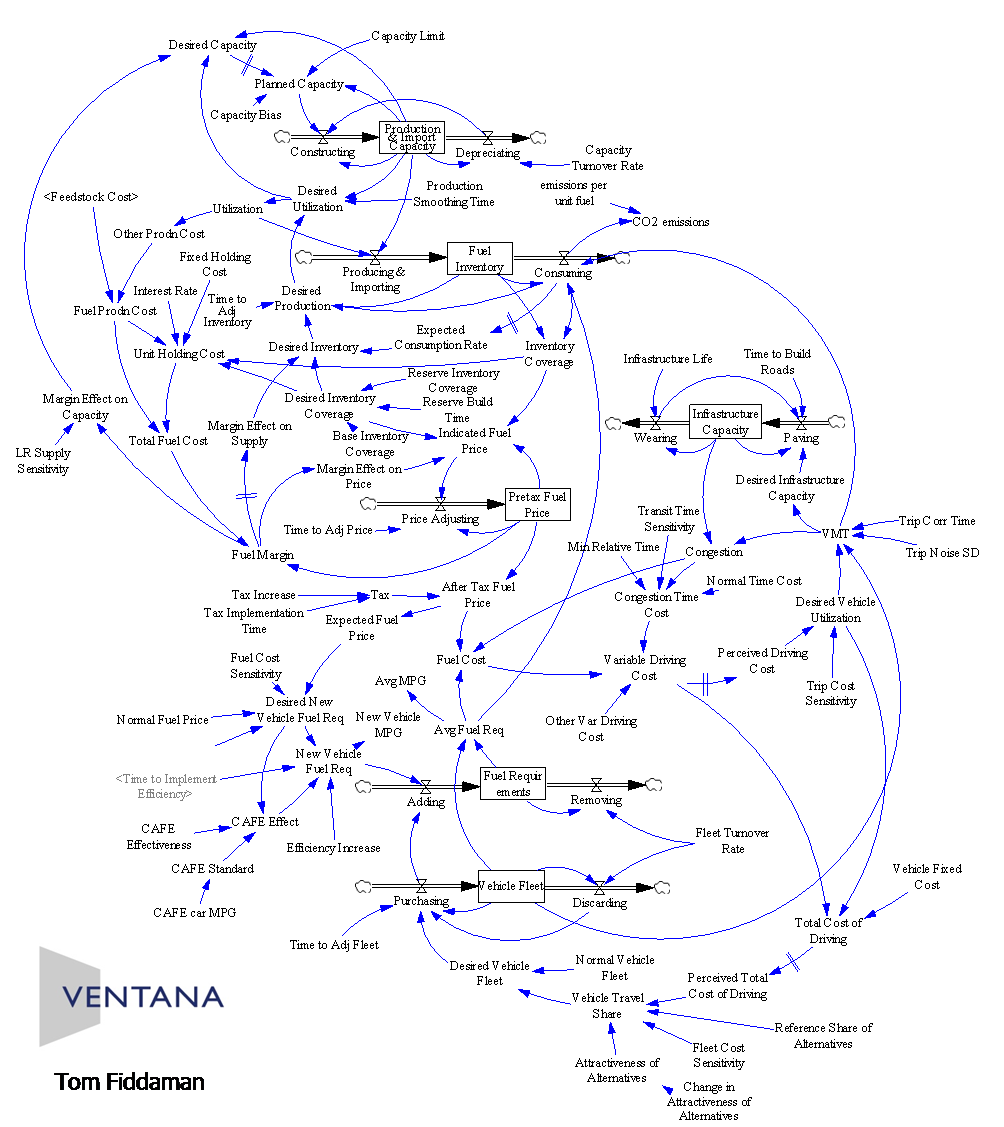

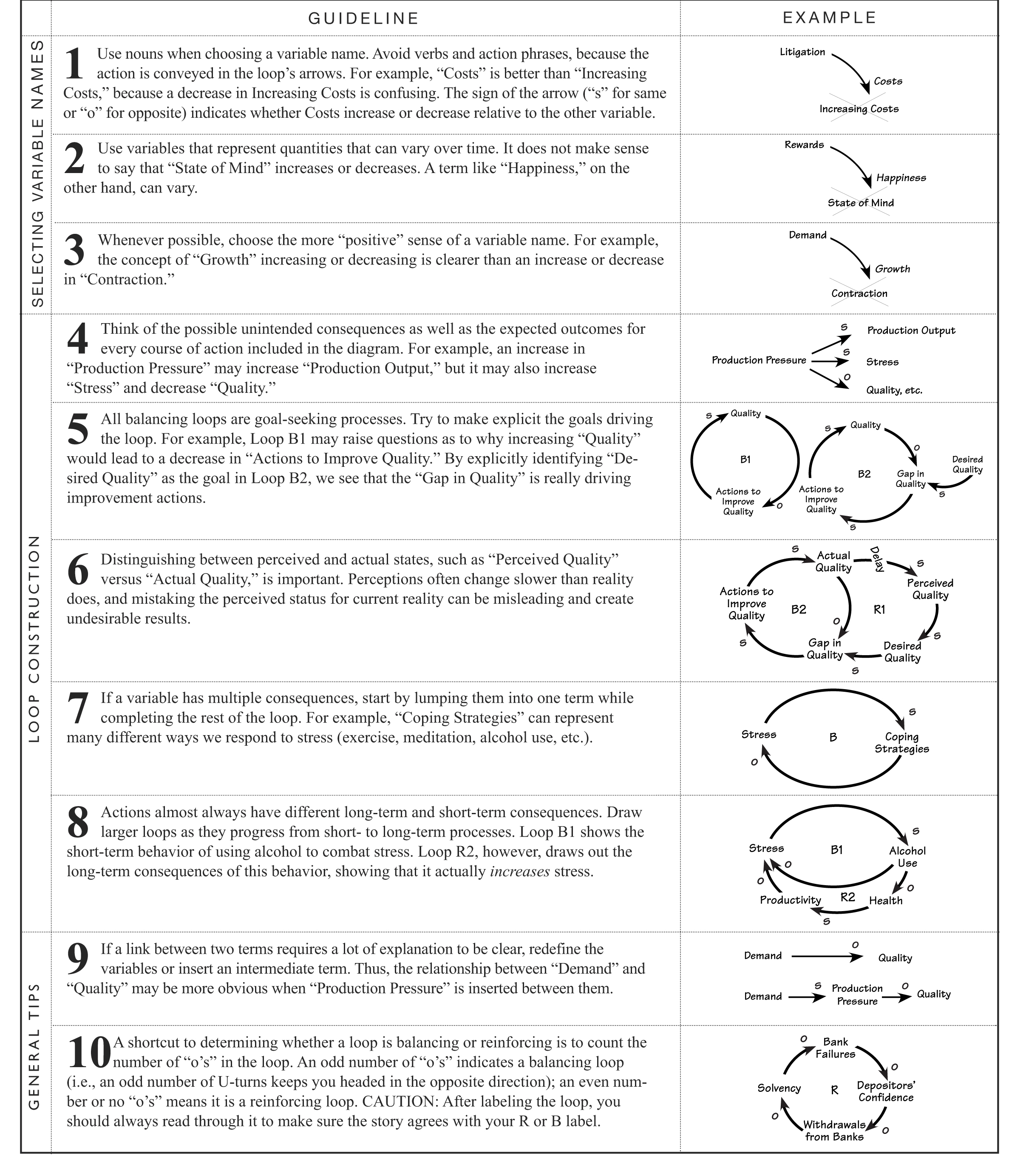

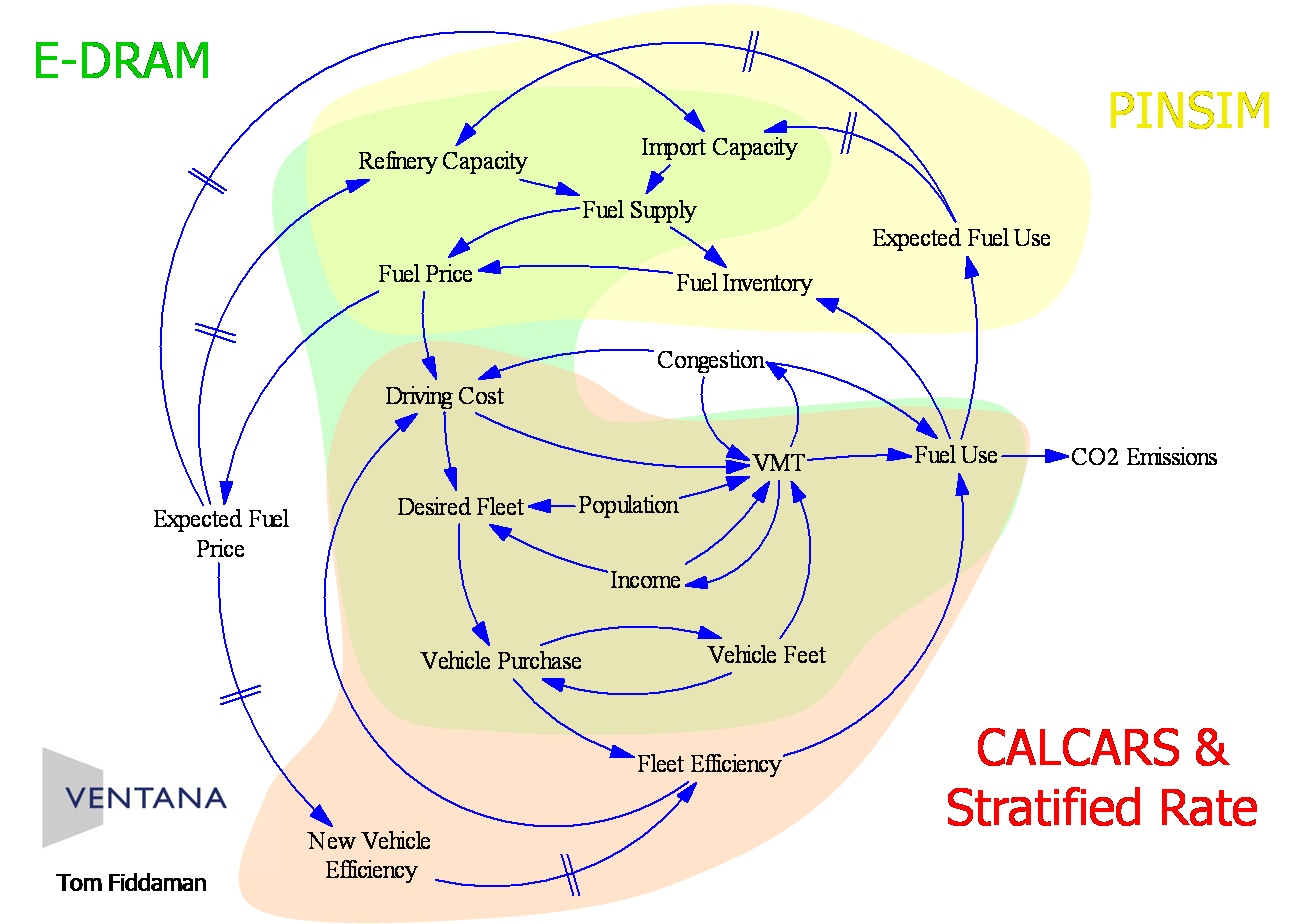

The **design philosophy** behind schematics is built on clarity and hierarchy. Circuits are grouped into functional blocks: power supply, control, signal processing, and actuation. Each block performs a task but interacts with others through shared nodes. For example, a relay circuit draws power from the supply section, control from a sensor, and output to an actuator. Grouping related elements in this way ensures the diagram remains readable, even as complexity increases.

Every symbol has meaningstandardized globally by conventions such as **IEC 60617** or **ANSI Y32.2**. These standards let an engineer in Japan read a diagram drawn in Germany without confusion. A resistor limits current, a diode allows one-way flow, and a transistor switches or amplifies signals. Once you learn these symbols, you can translate abstract shapes into real, physical components.

Lines and junctions act as the **arteries and intersections** of a circuit. A straight line shows a conductor, while a dot marks a connection. Lines that cross without a dot are *not* connecteda small detail that prevents costly mistakes. Wire numbering and color coding give additional identification, showing exactly how cables should be routed and labeled during assembly.

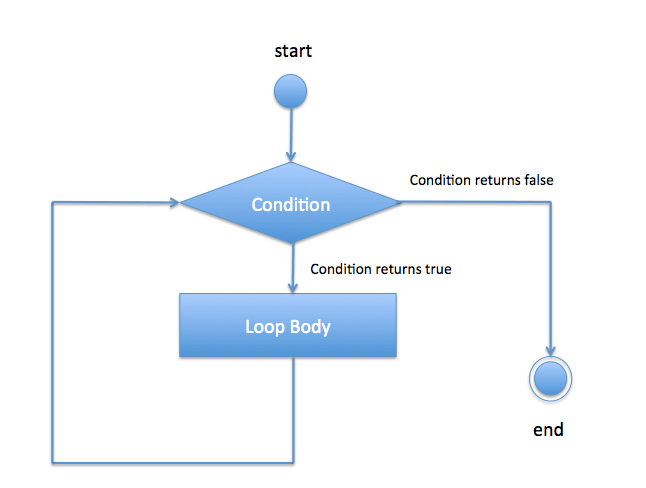

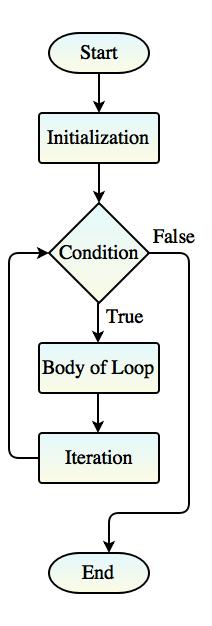

Modern schematics also include **logical and digital behavior**. In control systems, logic gates such as AND, OR, and NOT determine how signals interact. A relay may only energize when two separate inputs are activean electrical AND condition. Understanding these logic patterns helps predict system reactions, especially in automated or programmable environments.

Engineers design schematics not only for clarity but also for **maintainability**. During planning, they consider how future technicians will diagnose faults. Each connector, pin number, and component reference is labeled precisely. A good schematic doesnt just show how a system worksit also hints at how it might fail. This foresight simplifies troubleshooting and prevents confusion during repairs.

Another critical aspect is **signal grounding and reference potential**. In complex designs, different sections may share common grounds or use isolated ones to prevent interference. For example, analog sensors often have separate grounds from high-current motor circuits. Proper grounding paths ensure stable readings and reliable communication, especially in systems using mixed analog and digital signals.

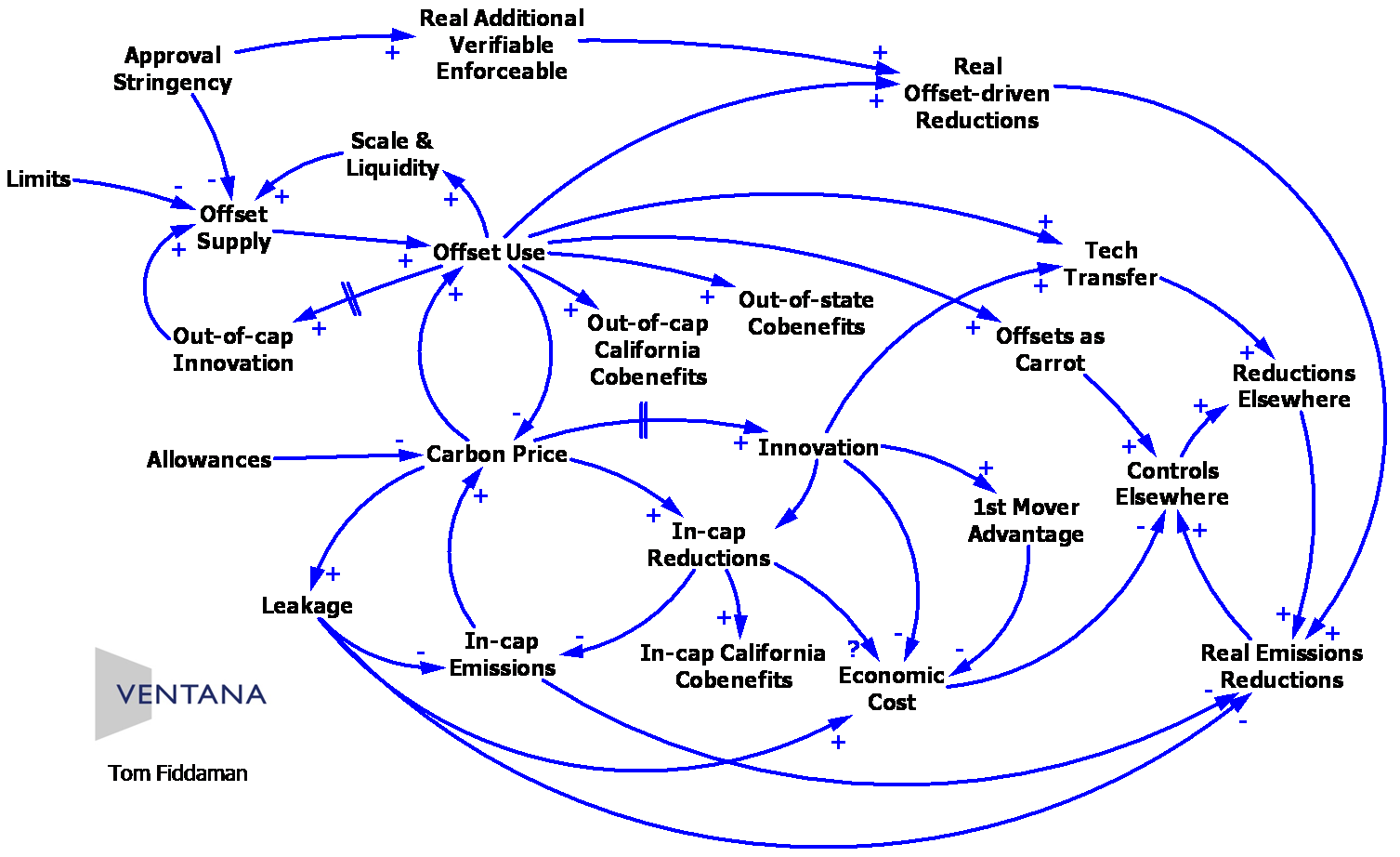

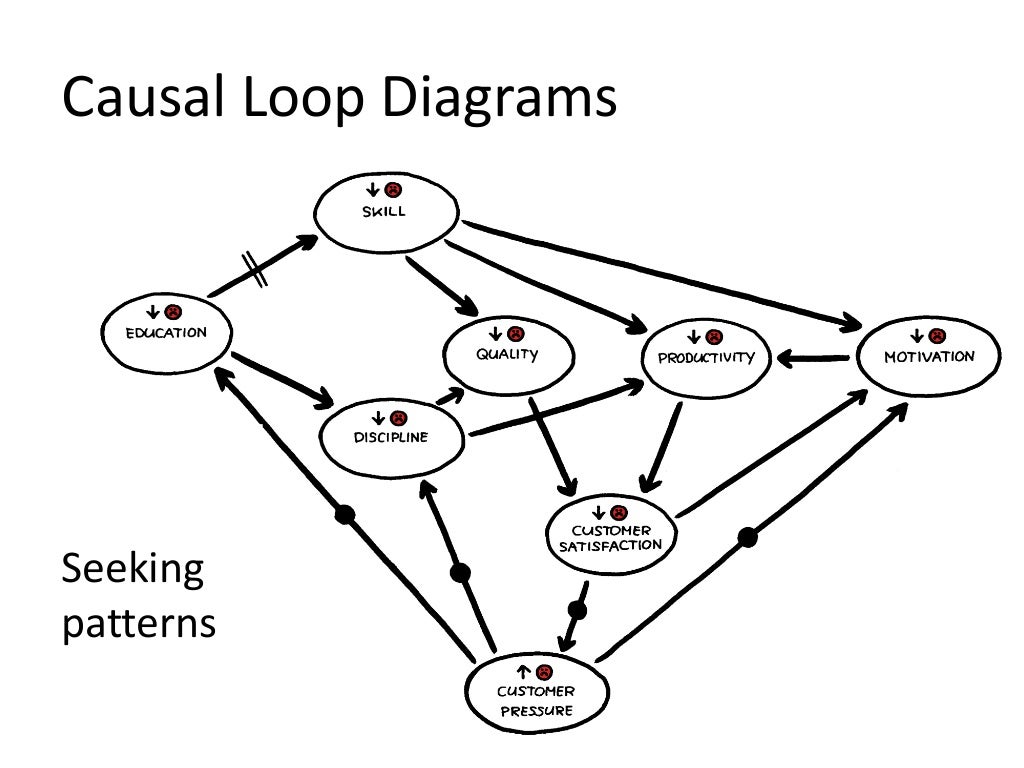

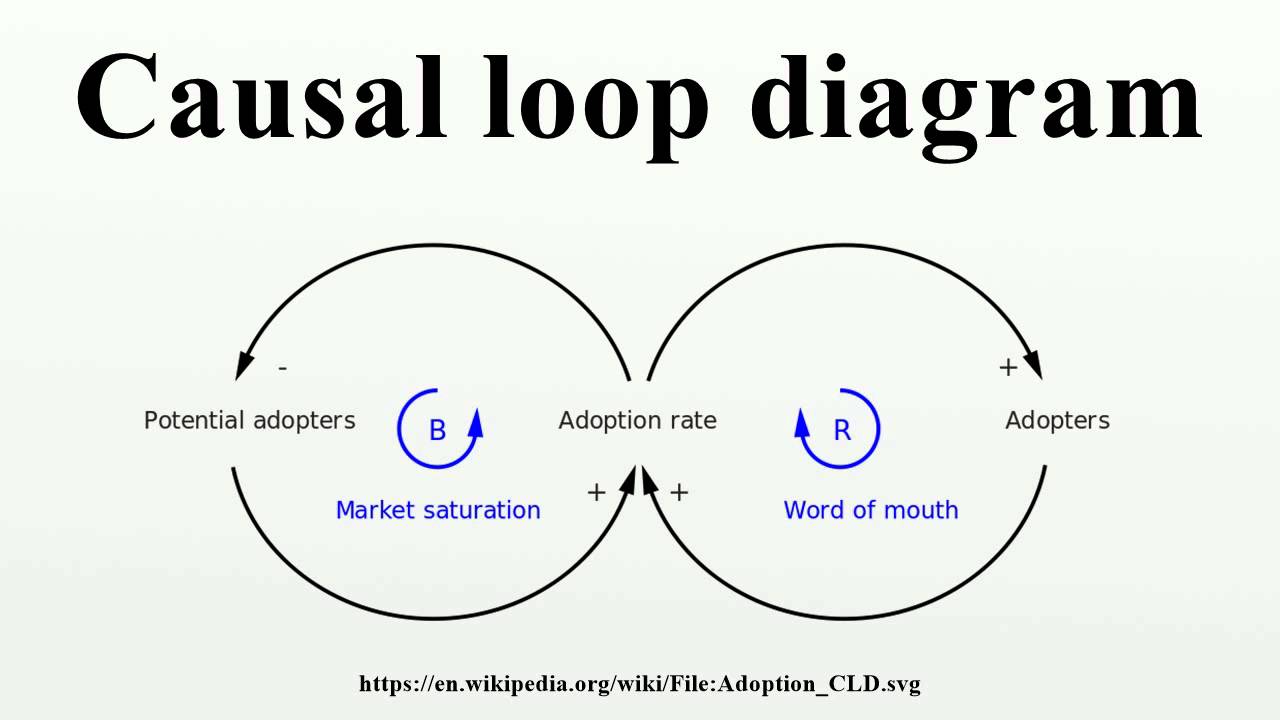

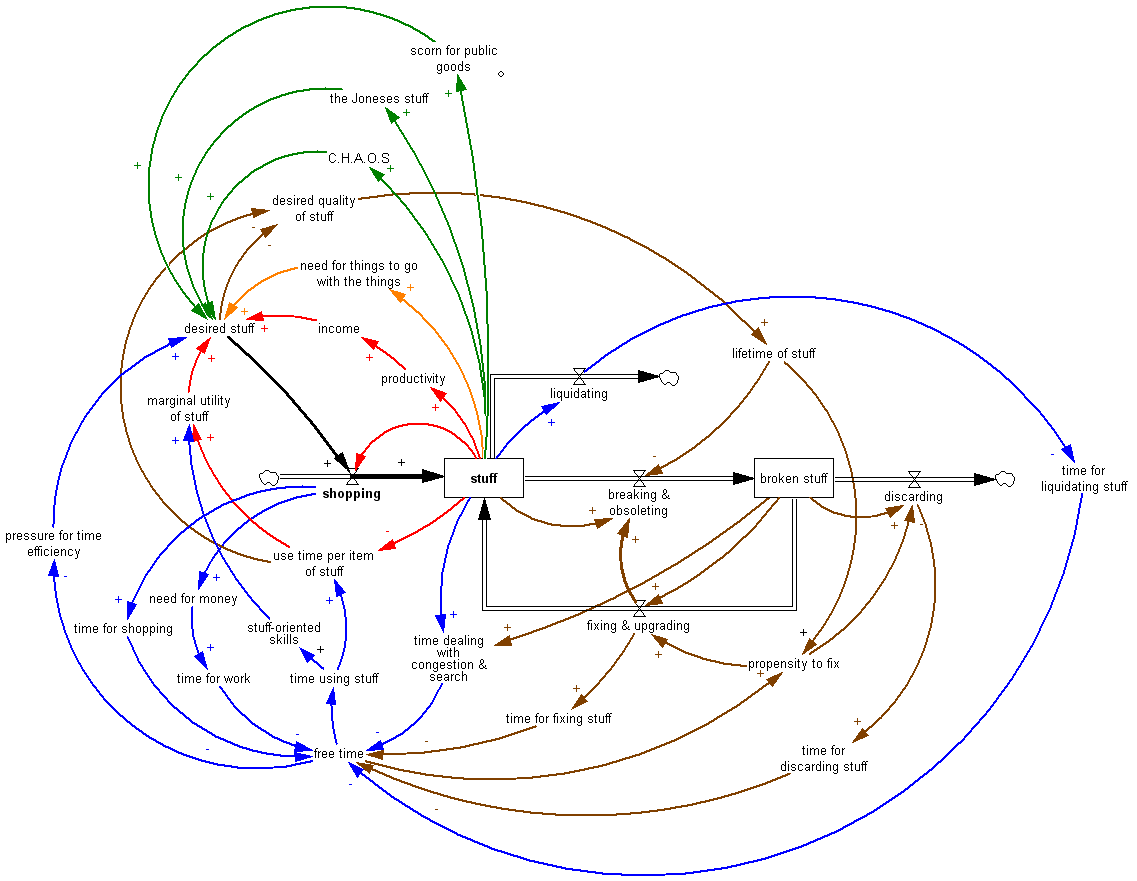

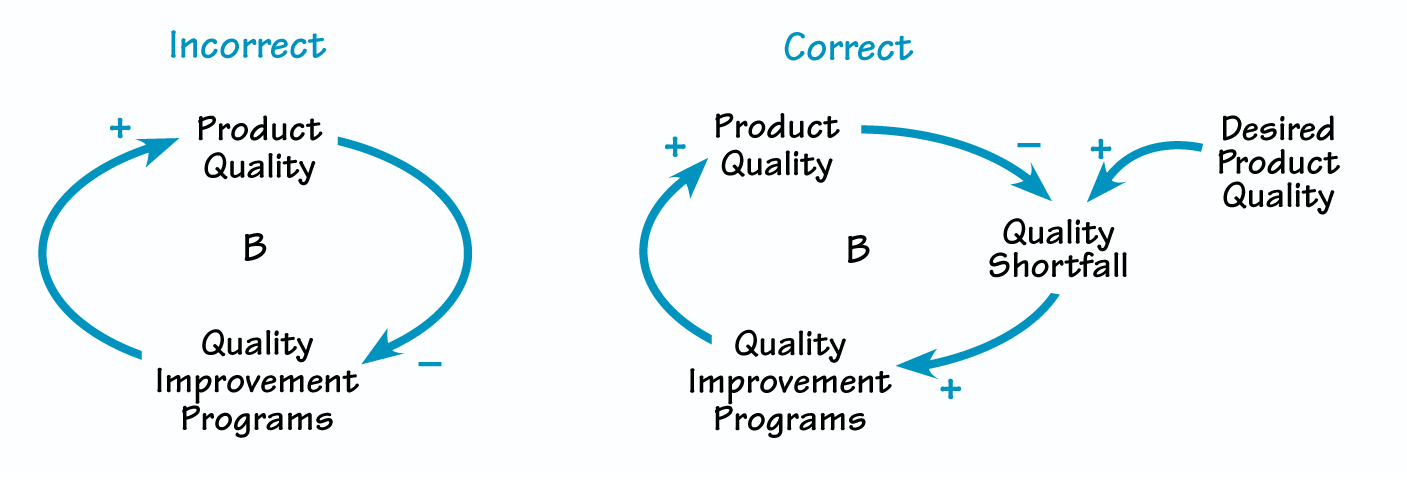

**Feedback loops** are another hallmark of good design. In motor control circuits, sensors monitor speed or position and send data back to controllers. The schematic represents this feedback with arrows or return lines, showing forward motion for action and backward flow for correction. Recognizing these loops reveals how systems maintain precision and self-balancekey concepts engineers rely on when refining automation.

Color codes provide real-world translation. Though schematics are usually monochrome, color references tell installers which wires to use. Red commonly means power, black for ground, and yellow or green for signals. Adhering to color standards reduces confusion during wiring, particularly when multiple technicians collaborate on the same equipment.

Beyond individual symbols, schematic logic extends into **system-level design**. For instance, in automotive networks, multiple modules communicate over shared buses like CAN or LIN. Each module has power, ground, and communication lines drawn in parallel, illustrating the entire networks architecture. This view helps identify interdependencieshow one modules failure might cascade to another.

Ultimately, schematic design is about **functional clarity**, not decoration. A good schematic tells a storyeven to someone unfamiliar with the system. You should be able to glance at it and understand where power starts, how signals move, and how components contribute to the bigger picture.

Studying schematic logic trains you to **think like an engineer**. Youll begin to recognize patterns: relays combining control and protection, sensors feeding data to controllers, and actuators executing those commands. Once you see these relationships, even the most complex wiring diagrams become logical and predictable.

The true beauty of electrical design lies in its invisible precision. Every line, every symbol, represents intentional thoughtturning raw energy into purposeful control. When you learn to read schematics with understanding, youre not just decoding diagramsyoure seeing the **blueprint of how machines think**. Thats the philosophy behind Electrical Loop Diagrams, an essential guide distributed through http://mydiagram.online in 2026 for professionals and enthusiasts across Loop Diagrams.